## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

Department of Electrical Engineering and Computer Science

## 6.012 MICROELECTRONIC DEVICES AND CIRCUITS

Problem Set No. 7

Issued: October 21, 2009

**Due:** October 28, 2009

## **<u>Reading Assignments:</u>**

Lecture 12 (10/22/09) - Notes Lecture 13 (10/27/09) - Chap. 7 (7.4.2); Chap. 8 (8.2.2a, 8.2.3); Chap. 10 (10.1.2a and c) Lecture 14 (10/29/09) - Chap. 15 (15.1)

<u>Problem 1</u> - Consider an n-channel silicon MOSFET and a p-channel silicon MOSFET which are identical in all dimensions and doping level magnitudes <u>except</u> that the <u>gate</u> <u>length</u>, L, of one of the devices is <u>twice</u> that of the other. The K-factors in the large signal characteristics are also identical. [The K-factor is defined as  $(W/L)\mu(\varepsilon_{ox}/t_{ox})$ .]

- (i) Which transistor, if either, would you expect to be the one with the longer gate length, and why?

- (ii) What is the ratio of the electron to hole mobility in these transistors (i.e., what is the ratio of the mobility of the electrons in the channel of the n-channel MOSFET to that of the holes in the channel of the p-channel MOSFET)? Explain.

- (iii) Which transistor, if either, has the larger small-signal gate-to-source capacitance in saturation, C<sub>gs</sub>? Explain your answer.

- (iv) Which transistor, if either, has the larger small-signal gate-to-drain capacitance in saturation, C<sub>gd</sub>? Explain your answer.

- (v) Both transistors are biased in saturation so they have the same magnitude of quiescent drain current, I<sub>D</sub>. Which transistor, if either, has the largest smallsignal transconductance, g<sub>m</sub>? Explain your answer and estimate the ratio of the two g<sub>m</sub>'s.

- (vi) Which transistor, if either, has a larger Early voltage, V<sub>A</sub>? Explain your answer.

- <u>Problem 2</u> This problems examines and compares (or contrasts) the sub-threshold and strong inversion operation of an n-channel MOSFET like the one we used as the example in Lecture 12. As you will recall, that device had  $t_{ox} = 3$  nm and  $N_A = 10^{18}$  cm<sup>-3</sup>. This resulted in having  $n = \alpha = 1.25$ . Assume that it also the electrostatic potential of the gate metal (degenerately n-doped poly-crystalline silicon) is 0.55 Volts, the channel length is 100 nm, and the electron mobility in the channel is 800 cm<sup>2</sup>/V-s.

- (a) What are the flat-band and threshold voltages of this device when  $v_{BS} = 0$ ?

- (b) (i) What is the factor  $\gamma$  (which was defined just before Problem 3 on Problem Set 6) for this device? This factor is called the "body factor" and is a gauge of how much the threshold voltage changes with substrate (body) bias,  $v_{BS}$ .

- (ii) What is the threshold voltage if  $v_{BS} = -1$  Volt?

- (c) How wide must the gate be to have  $K = 1 \text{ mA}/V^2$ ? (Remember to include  $\alpha$ .)

- (d) What is the drain current in saturation when this device is biased 1 Volt <u>above</u> threshold?

- (e) (i) What is the drain current in saturation when this device is biased 0.12 Volts <u>below</u> threshold?

- (ii) What is the drain current in saturation when  $v_{GS} = v_{BS} = 0$ ?

(iii) How much power is dissipated in an integrated circuit containing  $10^6$  transistors like this, each in series with a load connecting a 1.5 V power supply buss to ground [as, for example, in Figure 15.2(c) in the course text] when all of the transistors are off with  $v_{GS} = 0$ ?

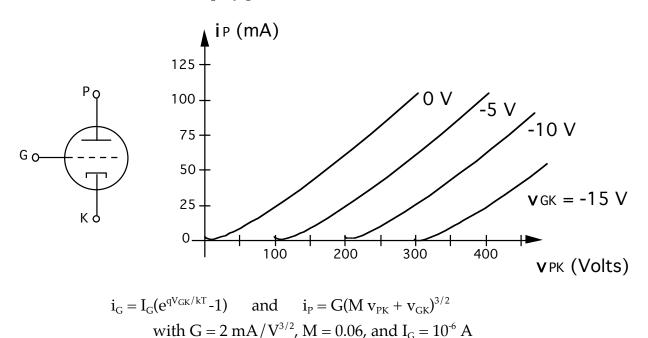

<u>Problem 3</u> - Several three-terminal devices (e.g., vacuum tube triodes, static induction transistors, field-emitter display pixels) have characteristics like those illustrated below:

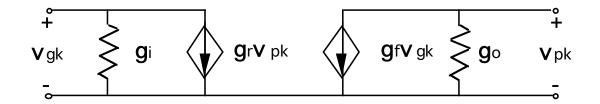

(a) An incremental model for a device with these characteristics is illustrated below.

Find mathematical expressions for each of the parameters in the incremental model ( $g_{i'}$ ,  $g_{r'}$ ,  $g_{f'}$ , and  $g_o$ ) and evaluate these expressions at the bias point  $V_{GK} = -4 \text{ V}$ , and  $V_{PK} = 160 \text{ V}$ .

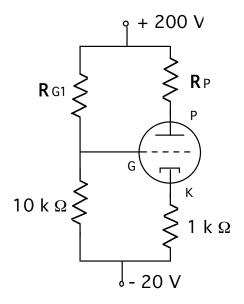

(b) This device is biased using the resistor bias circuit illustrated below:

Select  $R_{G1}$  and  $R_P$  to achieve the bias point specified in Part (a), i.e.,  $V_{GK} = -4 V$ , and  $V_{PK} = 160 V$ .

<u>Problem 4</u> ("iLab" problem) - This problem requires that you use a remote-control device measurement and characterization system called "iLab". Go to <u>http://ilab.mit.edu</u>, sign up for a user account if you don't have one already (this can take a day or two, so sign up well before this problem set is due), and read the user manual provided there. After reading the manual, go to "Launch Lab" and make your measurements using the Java applet that appears.

You select the device that will be under test from the "Device" menu. For this problem use one of the two devices named "3u nMOSFET" (#4 and #6).

Look at the output characteristics of this device as directed below. Prepare and submit the plots requested, and give the requested parameter values.

<u>Caution</u>: Do not let  $v_{GS}$  exceed 3 V or  $v_{DS}$  exceed 4 V.

- a) On linear scales, plot  $i_D vs v_{DS}$  for  $0 \le v_{DS} < 4 V$ , with  $v_{GS}$  as a parameter ( $0 \le v_{GS} \le 3 V$ ) and with  $v_{BS} = 0$ . Estimate the threshold voltage,  $V_T$ , and the Early voltage,  $V_A$ , for this device.

- b) Repeat Part (b) with  $v_{BS} = -0.5$  V.

- c) Plot  $i_D$  vs  $v_{GS}$ , with  $v_{DS} = 4$  V and  $v_{BS} = 0$  V on a linear scale. Also plot  $(i_D)^{1/2}$  vs  $v_{GS'}$  and use this plot to find the threshold voltage,  $V_T$ , and the K-factor of this device with  $v_{BS} = 0$ .

- d) Display the plot of  $i_D vs v_{GS}$ , with  $v_{DS} = 4 V$  and  $v_{BS} = 0 V$  in Part (c) on a log-linear scale and use it to estimate the sub-threshold slope and the value of "n". Also determine the factor  $I_{S,s-t}$  in the expression for sub-threshold current (see, for example, Slide 21 in Lecture 12).

e) Use the techniques in Parts (c) and (d) to estimate the threshold voltage, sub-threshold slope, the factor  $I_{S,s-\nu}$  and "n" when  $v_{BS} = -0.5$  V.

Comment on whether the changes you find from the  $v_{BS} = 0$  case have the right sign, and whether they seem reasonable.

- f) Return to your plot of  $i_D vs v_{DS}$  for  $0 \le v_{DS} < 4 V$ , with  $v_{GS}$  as a parameter ( $0 \le v_{GS} \le 3 V$ ) and with  $v_{BS} = 0$  in Part (a), but only plot it for ( $0 \le v_{GS} \le V_T$ ), and make it a log-linear plot, i.e., log  $i_D vs v_{DS}$ . You might even try to make the steps in  $v_{GS}$  be nkT/q, and compare your plot to that on Slide 26 of Lecture 12.

- g) <u>Optional extra fun</u> (I am curious to see what you find): Your estimates of K, n, and  $I_{ss-t}$  in Part (d) should all be consistent, and in fact should be related (see Slide 21 of Lecture 12). You should find:  $I_{s,s-t} = K_o (kT/q)^2$  (n-1). What do you actually find?

Note: The estimates you found in Part (e) should, of course, also be related. You may want to check that too.

## Additional final comments on iLab:

The "auto scale" function might be useful for displaying plots.

For research purposes, the system keeps a record of all logins and all scripts that each user executes.

6.012 Microelectronic Devices and Circuits Fall 2009

For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.