# 6.012 - Microelectronic Devices and Circuits Spring 2006 Design Problem Circuit

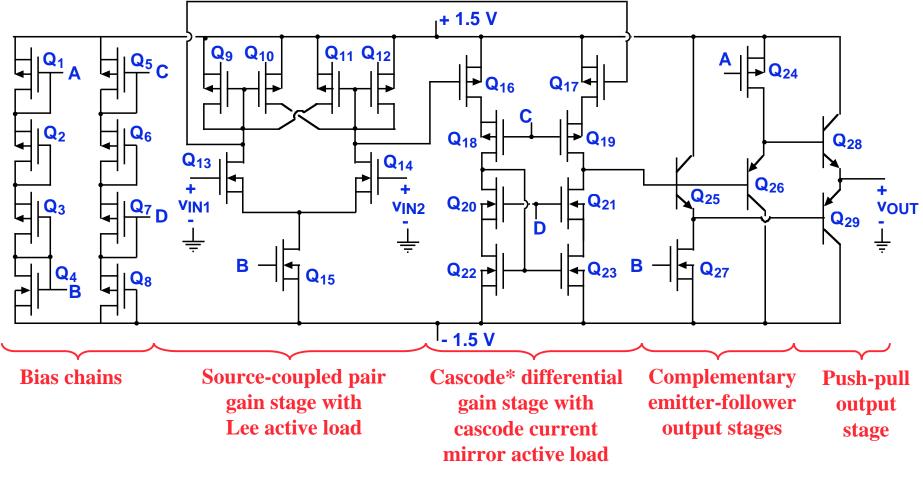

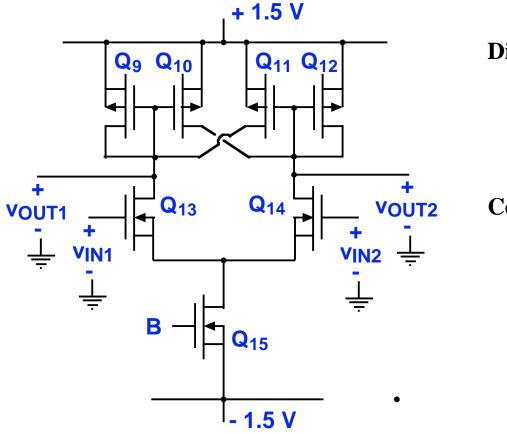

# **Full schematic**

\* Common source stage followed by common base stage.

6.012 Design Problem

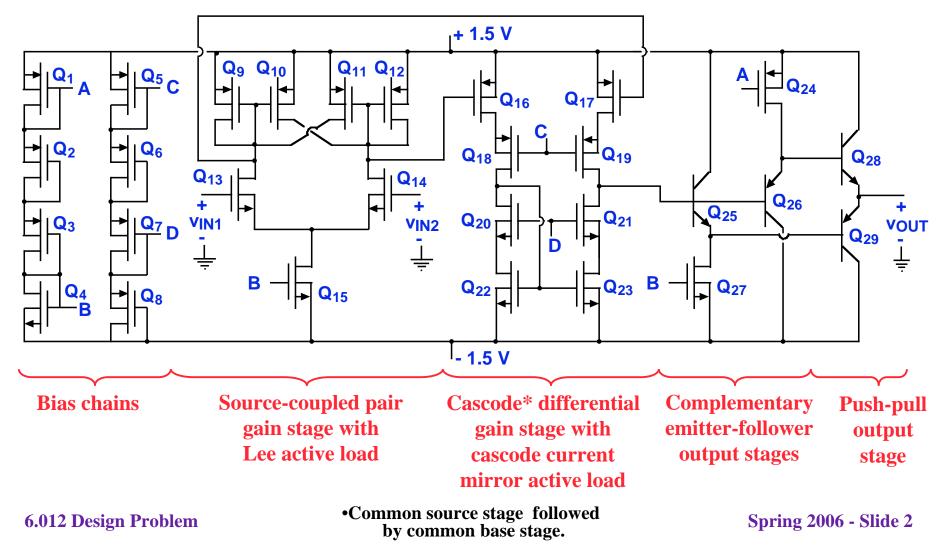

## **Circuit drawn with alternative MOSFET symbols:**

Some find the MOSFET symbols used in this version of the schematic with the arrow on the source, rather than the gate, more intuitive when looking at a schematic. The rest of the foils in this set use the <u>original symbols</u>, so this figure help you adapt those foils if you prefer these alternative symbols.

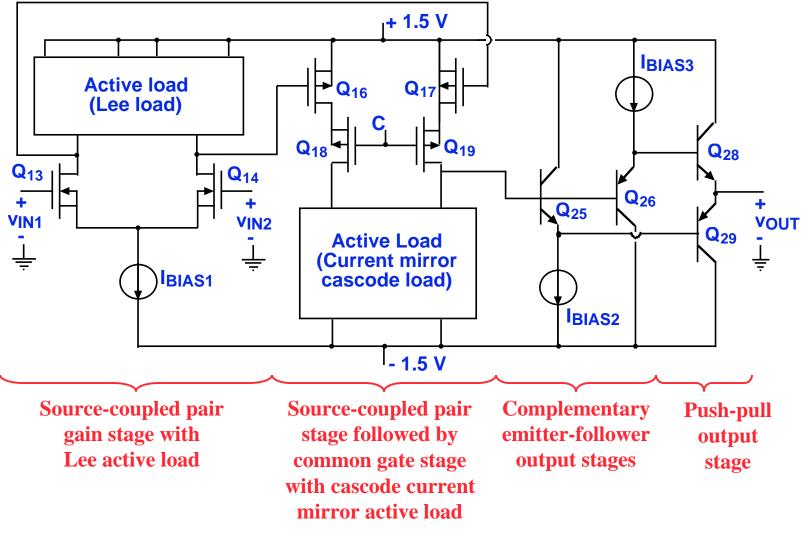

# **Conceptual schematic: full circuit**

**6.012 Design Problem**

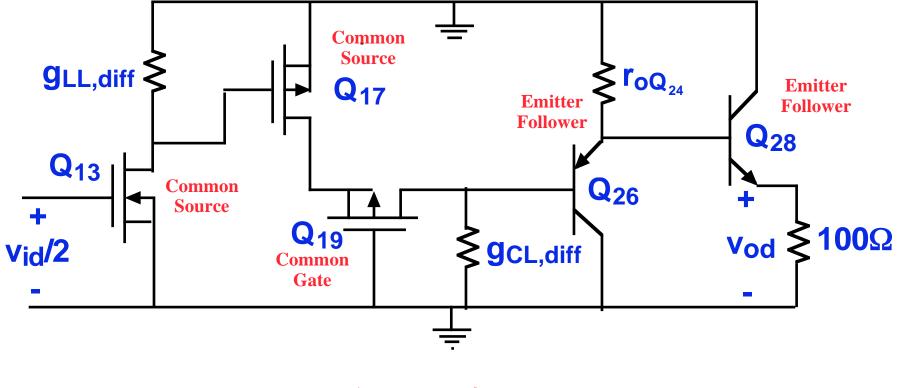

# **Conceptual schematic: difference-mode inputs**

$A_{vd} = v_{od}/v_{id}$

#### 6.012 Design Problem

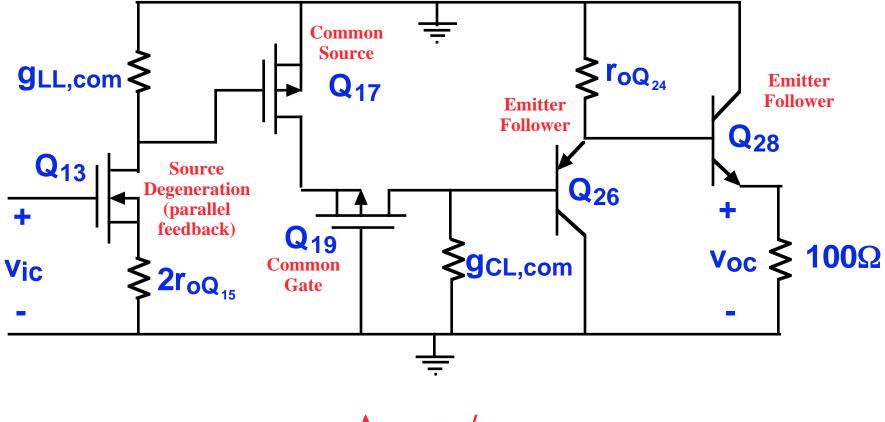

# **Conceptual schematic: common-mode inputs**

$A_{vc} = v_{oc}/v_{ic}$

#### 6.012 Design Problem

#### **Points to ponder:**

- What is the drain current of a minimum size n-channel MOSFET when  $(V_{GS}-V_T) = (V_{GS}-V_T)_{min}$ ? What is it for a minimally biased p-channel MOSFET?

- How can  $Q_1$  and  $Q_4$  both be at this minimum bias point?

6.012 Design Problem

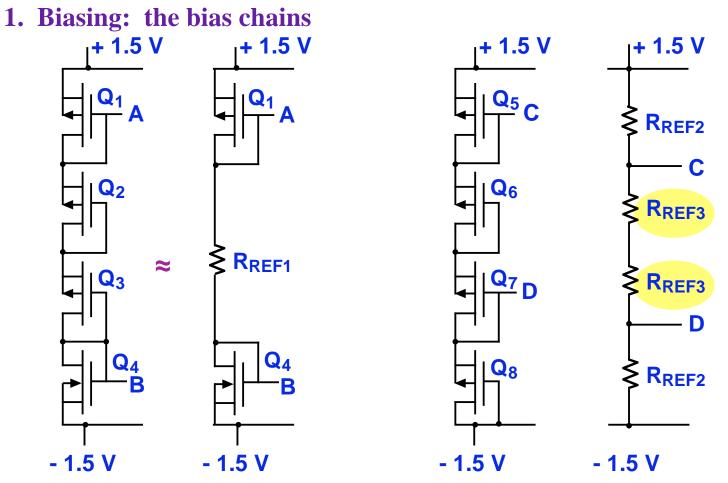

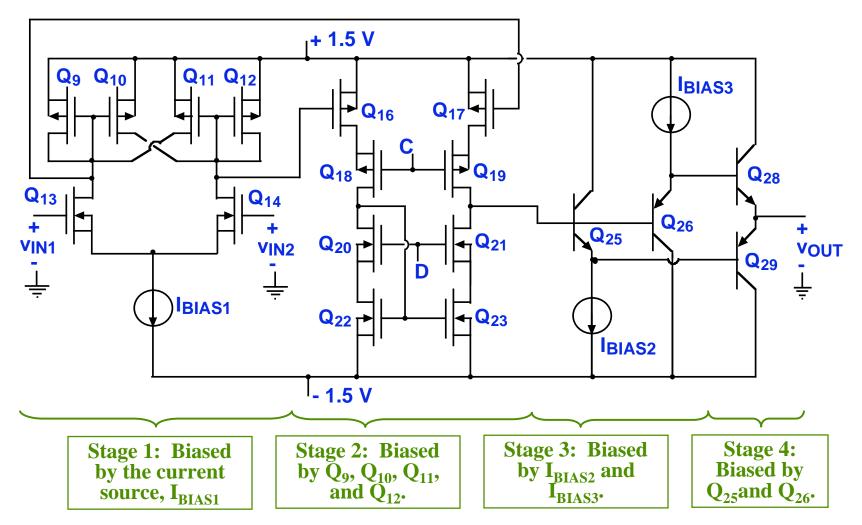

1. Biasing: looking at how each of the four stages is biased

**Point to ponder:**

6.012 Design Problem

- Stages 2 and 4 are biased by the preceding stages.

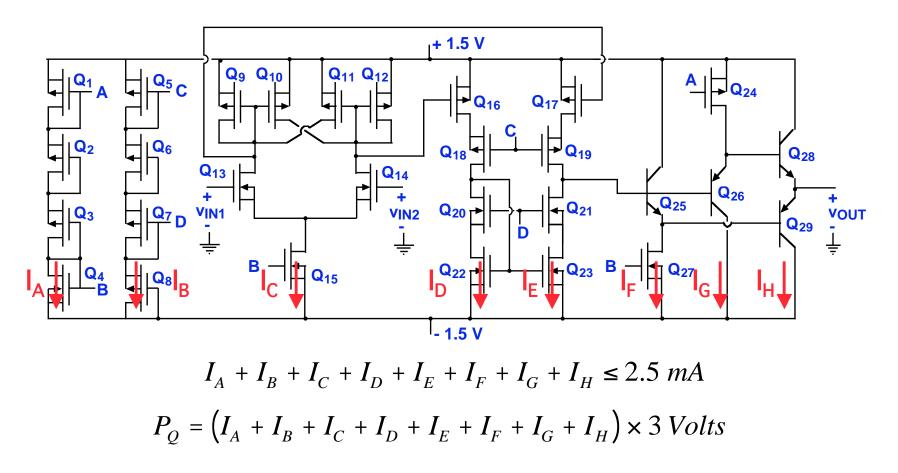

- **1. Biasing: power dissipation**

- A constraint on the bias currents is the total power dissipation specification of 7.5 mW. This means that the total bias current must be less that 2.5 mA (i.e,  $3 V \times 2.5 mA = 7.5 mW$ ).

6.012 Design Problem

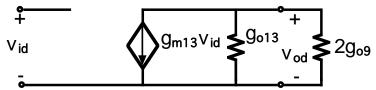

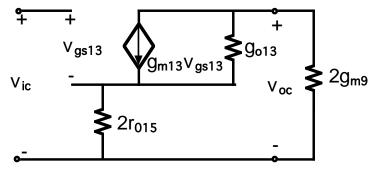

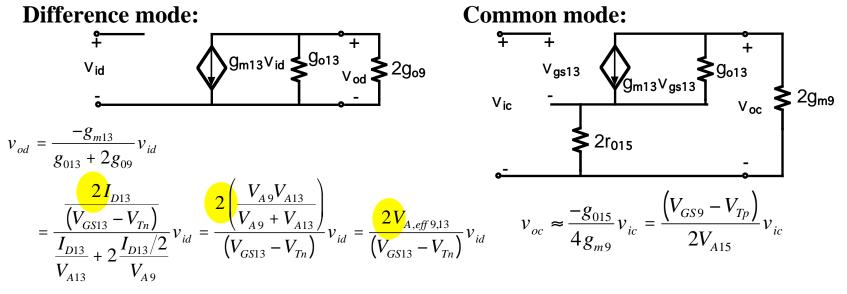

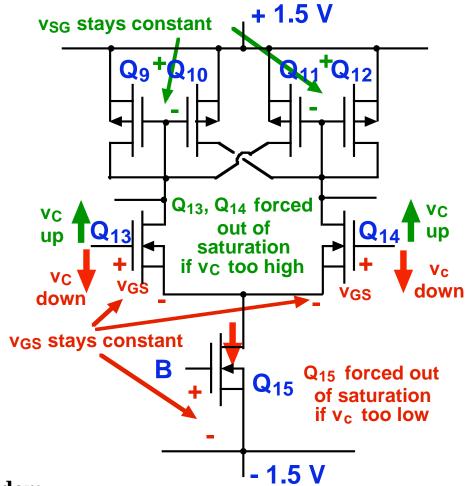

2. First gain stage: gain of source-coupled pair with Lee load

A Lee Load is an active load that looks different in common and difference mode. A full analysis can be found in the handout "Two Active Loads" posted on Stellar.

**Difference mode:**

**Common mode:**

6.012 Design Problem

2. First gain stage: gain of source-coupled pair with Lee load

**Combined:**

$$v_{out1} = \frac{-g_{m13}}{g_{o13} + 2g_{o9}} \cdot \frac{(v_{in1} - v_{in2})}{2} - \frac{g_{015}}{4g_{m9}} \cdot \frac{(v_{in1} + v_{in2})}{2} = \frac{-V_{A.eff\,9,13}}{(V_{GS13} - V_{Tn})} \cdot (v_{in1} - v_{in2}) - \frac{(V_{GS13} - V_{Tn})}{2V_{A15}} \cdot \frac{(v_{in1} + v_{in2})}{2} = \frac{g_{m13}}{(v_{GS13} - V_{Tn})} \cdot \frac{(v_{in1} - v_{in2})}{2} - \frac{g_{015}}{4g_{m9}} \cdot \frac{(v_{in1} + v_{in2})}{2} = \frac{V_{A.eff\,9,13}}{(V_{GS13} - V_{Tn})} \cdot (v_{in1} - v_{in2}) - \frac{(V_{GS13} - V_{Tn})}{2V_{A15}} \cdot \frac{(v_{in1} + v_{in2})}{2} = \frac{V_{A.eff\,9,13}}{(V_{GS13} - V_{Tn})} \cdot (v_{in1} - v_{in2}) - \frac{(V_{GS13} - V_{Tn})}{2V_{A15}} \cdot \frac{(v_{in1} + v_{in2})}{2} = \frac{V_{A.eff\,9,13}}{(V_{GS13} - V_{Tn})} \cdot \frac{(v_{in1} - v_{in2})}{2V_{A15}} \cdot \frac{(v_{in1} + v_{in2})}{2} = \frac{V_{A.eff\,9,13}}{(V_{GS13} - V_{Tn})} \cdot \frac{(v_{in1} - v_{in2})}{2V_{A15}} \cdot \frac{(v_{in1} + v_{in2})}{2} = \frac{V_{A.eff\,9,13}}{(V_{GS13} - V_{Tn})} \cdot \frac{(v_{in1} - v_{in2})}{2V_{A15}} \cdot \frac{(v_{in1} + v_{in2})}{2} = \frac{V_{A.eff\,9,13}}{(V_{GS13} - V_{Tn})} \cdot \frac{(v_{in1} - v_{in2})}{2V_{A15}} \cdot \frac{(v_{in1} + v_{in2})}{2} = \frac{V_{A.eff\,9,13}}{(V_{GS13} - V_{Tn})} \cdot \frac{(v_{in1} - v_{in2})}{2V_{A15}} \cdot \frac{(v_{in1} - v_{in2})}{2} = \frac{V_{A.eff\,9,13}}{(V_{GS13} - V_{Tn})} \cdot \frac{(v_{in1} - v_{in2})}{2V_{A15}} \cdot \frac{(v_{in1} - v_{in2})}{2} = \frac{V_{A.eff\,9,13}}{(V_{GS13} - V_{Tn})} \cdot \frac{(v_{in1} - v_{in2})}{2V_{A15}} \cdot \frac{(v_{in1} - v_{in2})}{2} = \frac{V_{A.eff\,9,13}}{(V_{GS13} - V_{Tn})} \cdot \frac{(v_{in1} - v_{in2})}{2V_{A15}} \cdot \frac{(v_{in1} - v_{in2})}{2} = \frac{(v_{in1}$$

**Points to ponder:**

- The outputs go to the gates of other MOSFET, so they do not load this stage. What does this about getting the maximum difference mode out of this stage?

- How can  $Q_9$  through  $Q_{15}$  all be biased at their minimum bias point?

6.012 Design Problem

2. First gain stage, cont: common-mode input range

#### **Point to ponder:**

- What is  $v_{\text{DS}}$  and what is  $v_{\text{GD}}$  at the boundary between the saturation and linear regions?

6.012 Design Problem

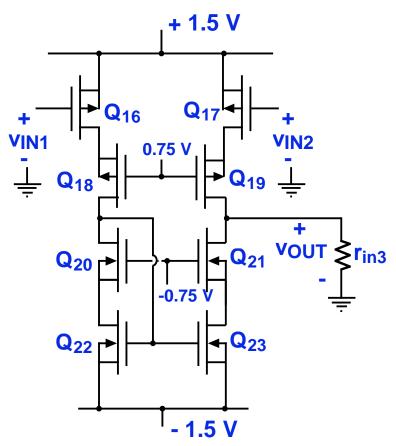

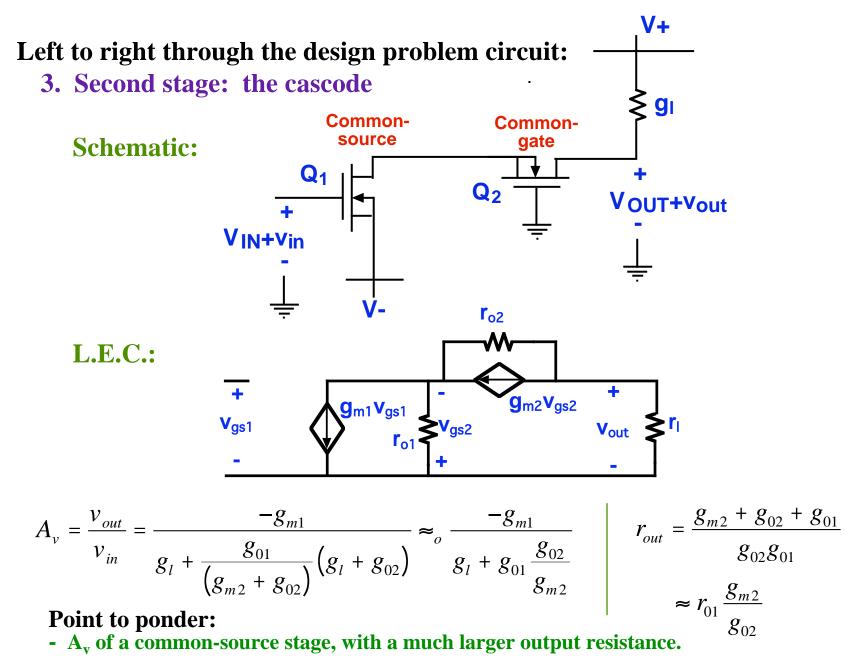

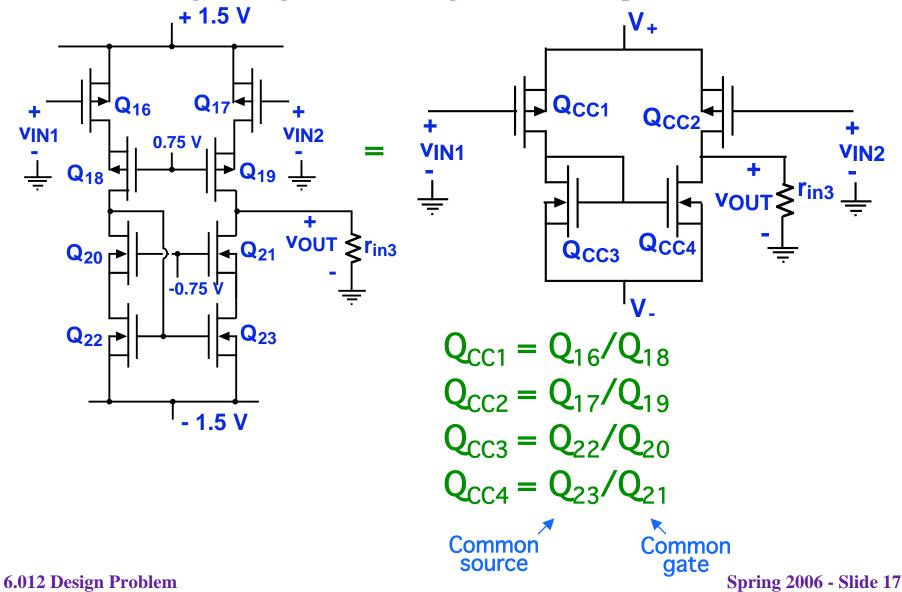

3. Second gain stage: source-coupled cascode, current mirror load

#### **Comments/Observations:**

- This stage is essentially a normal source-coupled pair with a current mirror load, but there are differences..

- The first difference is that two driver transistors are cascode pairs. The stage thus has two sub-stages, the first being a source-coupled pair which is loaded by the second, which is a common-gate pair. The combination of a common source stage followed by a common gate stage is called a "cascode.

- The second difference is that the current mirror load is also cascoded.

- The third difference is that the stage is not biased with a current mirror, but is instead biased by the first gain stage.

#### Point to ponder:

- Notice that output of the stage is loaded by the input resistance of the third stage. In the first stage there was no loading. How does this effect the gain and how we maximize it?

6.012 Design Problem

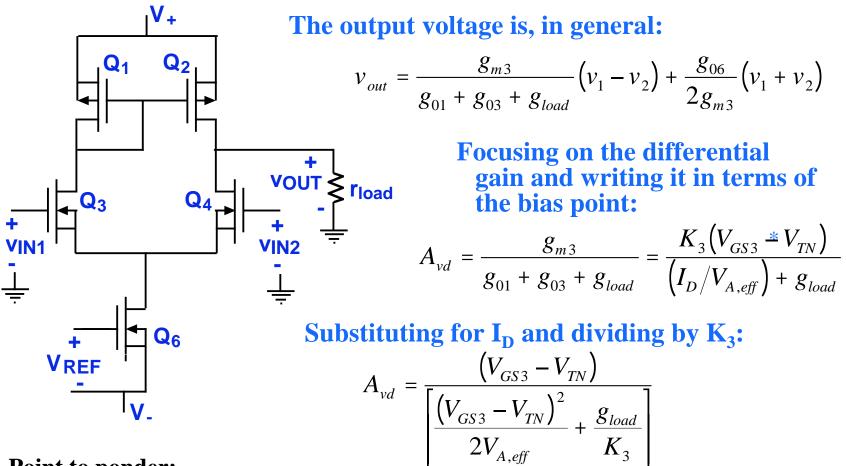

3. Second stage: gain of a simple current mirror with loading

#### **Point to ponder:**

- When the output is not loaded the voltage gain,  $2V_{A,eff}/(V_{GS3} - V_{TN})$ , does not depend on the K's of the transistors, but when it is loaded by  $r_{load}$ , making K bigger can increase the gain.

6.012 Design Problem

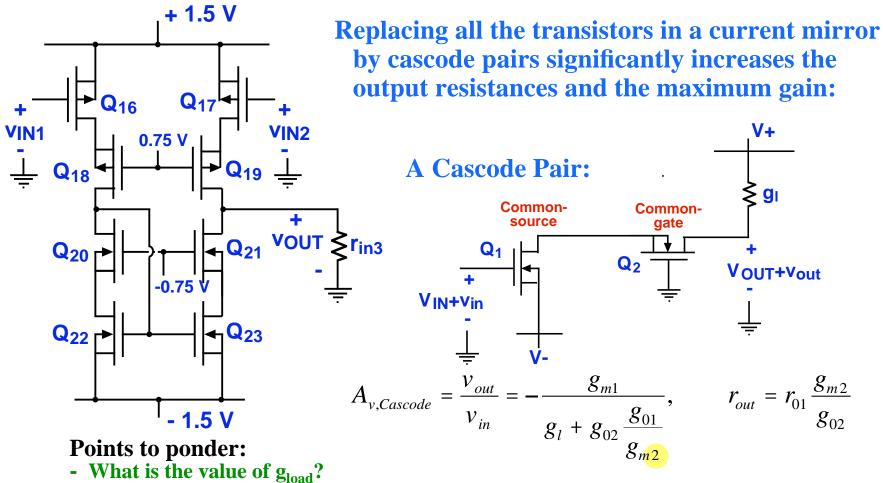

**3. Second stage: the impact of having cascode pairs**

- Is it feasible to bias  $Q_{16}^{16}$  and Q17 to get the largest gain? How close can one come?

- Changing the bias on  $\dot{Q}_{16}/\dot{Q}_{17}$  means that of  $\dot{Q}_{9}/\dot{Q}_{10}/\dot{Q}_{11}/\dot{Q}_{12}$  must change. Is this OK?

- How much can K be increased? Is there any disadvantage to making K this big?

- Over what range can v<sub>OUT</sub> swing (positive and negative)?

6.012 Design Problem

6.012 Design Problem

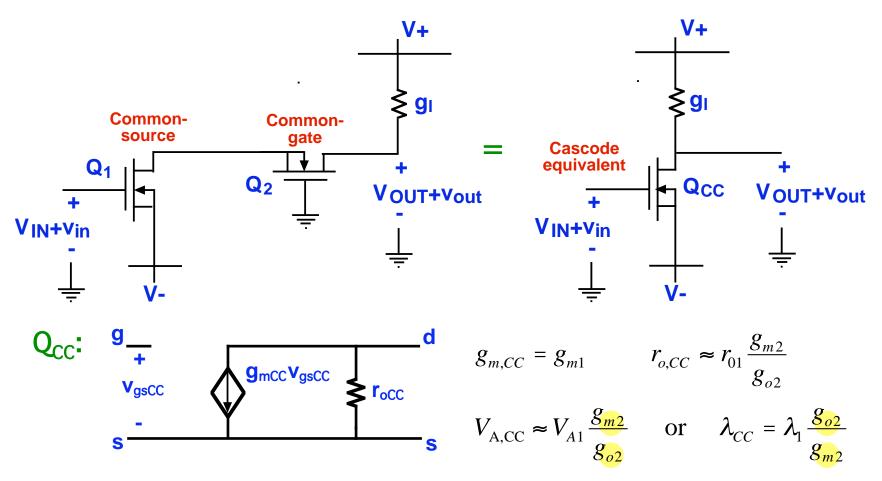

**3. Second stage: looking more at the cascode**

The cascode stage looks like a common source stage made of a special "cascode" transistor,  $Q_{CC}$ :

6.012 Design Problem

**3. Second gain stage: substituting the cascode equivalents**

3. Second gain stage: substituting the cascode equivalents

$$A_{vd} = v_{out} / (v_{in1} - v_{in2}) \text{ with } v_{in1} = v_{id} / 2, v_{in2} = -v_{id} / 2:$$

$$A_{vd} = \frac{2g_{m,CC2}}{g_{o,CC2} + g_{o,CC4} + g_{in3}} = \frac{2g_{m17}}{\binom{g_{o17}g_{o19}}{g_{m19}} + \binom{g_{o23}g_{o21}}{g_{m21}} + g_{in3}}$$

A<sub>vd</sub> continued on next foil

6.012 Design Problem

3. Second gain stage: completing the gain derivation  $A_{vd}$  cont.:

6.012 Design Problem

\* This may not be the peak gain, but it will be OK.

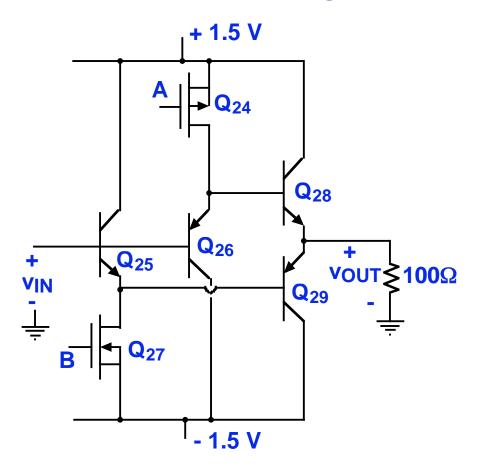

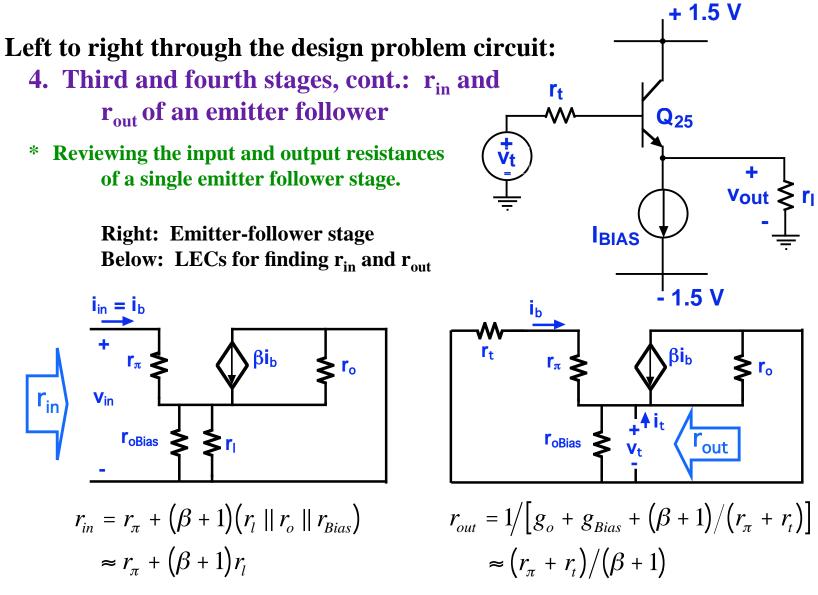

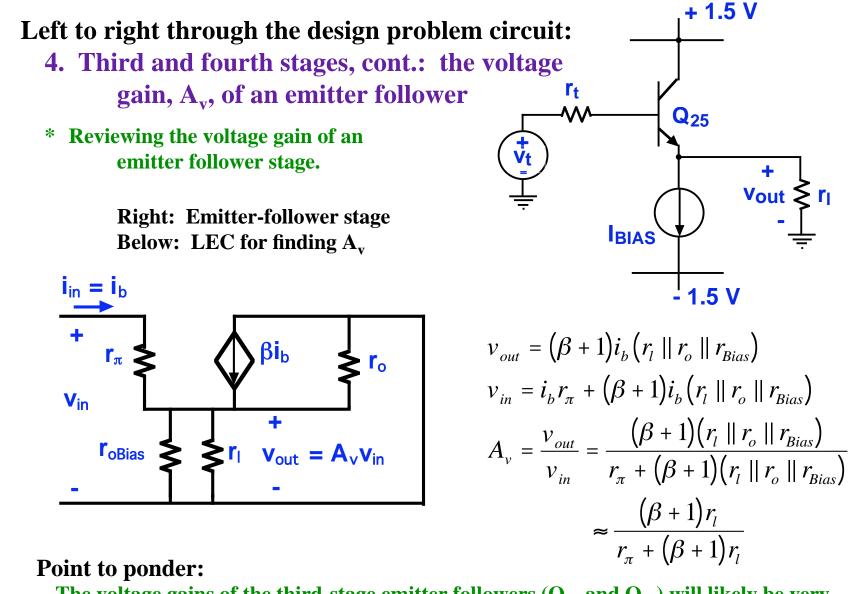

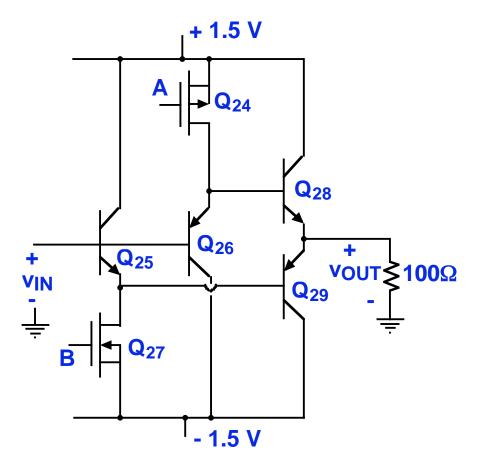

4. Third and fourth stages: emitter-followers

#### **Comments/Observations:**

- These stages involve four emitter follower building blocks arranged as two parallel cascades of two emitter follower stages each. These stages offer the most design challenges and trade-offs of any of the stages in the design problem.

- They must be biased properly taking into account KVL and KCL constraints.

- Although they have voltage gains of almost one, they have a big effect on the overall voltage gain of the amplifier because they load the second gain stage.

- They determine the output resistance of the amplifier.

Point to ponder:Am I having fun yet? (This is where the fun begins.)

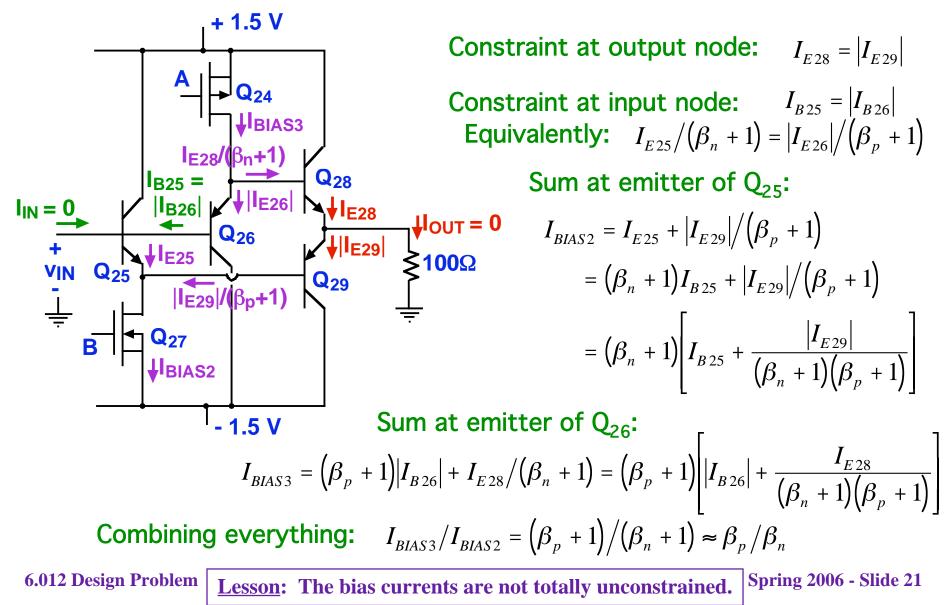

4. Third and fourth stages, cont.: biasing - getting the currents right

4. Third and fourth stages, cont.: biasing - getting the voltages right

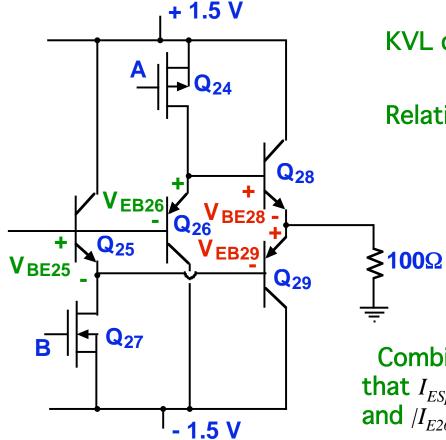

KVL constraint:

$$V_{BE\,28} + V_{EB\,29} - V_{BE\,25} - V_{EB\,26} = 0$$

Relating voltages to currents:

$$V_{BE25} = (kT/q) \ln[I_{E25}/\gamma_{25}I_{ESn}]$$

$$V_{EB26} = (kT/q) \ln[|I_{E26}|/\gamma_{26}I_{ESp}]$$

$$V_{BE28} = (kT/q) \ln[I_{E28}/\gamma_{28}I_{ESn}]$$

$$V_{BE29} = (kT/q) \ln[|I_{E29}|/\gamma_{29}I_{ESp}]$$

Combining everything, including the fact that  $I_{ESp} = I_{ESn} = I_{ES}$ , and the results  $|I_{E28}| = I_{E29}$  and  $|I_{E26}|/(\beta_p + 1) = I_{E25}/(\beta_n + 1)$ , yields:

$\frac{I_{E28}}{I_{E25}} = \sqrt{\frac{(\beta_p + 1)}{(\beta_n + 1)}} \frac{\gamma_{28}\gamma_{29}}{\gamma_{25}\gamma_{26}}$

Point to ponder:What do the results on this foil and the last mean, and are there any other things to consider when biasing these stages?

6.012 Design Problem

Lesson: The BJT areas matter.

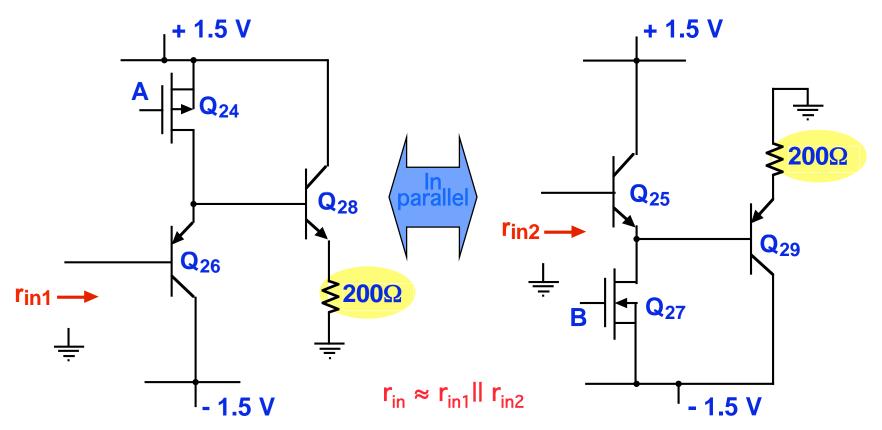

4. Third and fourth stages, cont.: input resistance, r<sub>in</sub>

We will use the approximation that the two emitter-follower paths can be modeled as being in parallel for purposes of calculating the input resistance.

**Point to ponder:**

- Remember that the ratio of  $I_{BIAS3}$  to  $I_{BIAS4}$  is constrained.

- Is there a penalty for picking a bias that maximizes  $r_{in}$ ? What else would be impacted?

6.012 Design Problem

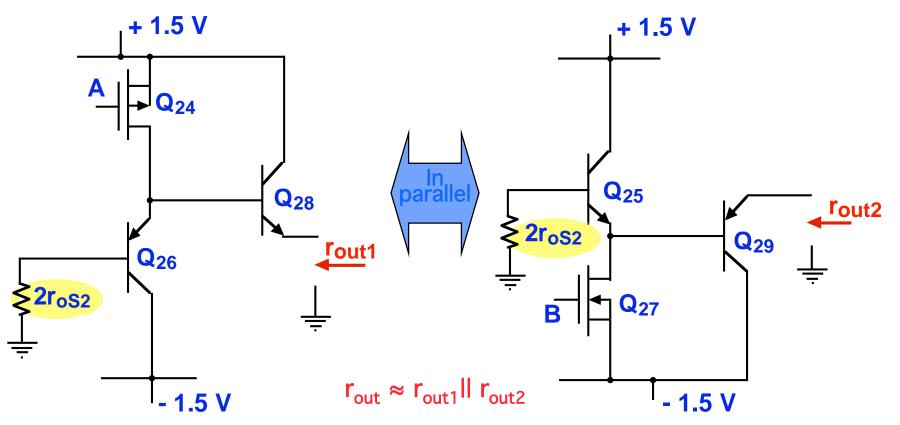

4. Third and fourth stages, cont.: output resistance, r<sub>out</sub>

\* We will use the approximation that the two emitter-follower paths can be modeled as being in parallel for purposes of calculating the output resistance.

Point to ponder:

- Remember that the ratio of  $I_{BIAS3}$  to  $I_{BIAS4}$  is constrained.

- Is there a trade-off between power dissipation and  $r_{out}$ ? Is there an optimum bias?

6.012 Design Problem

**Point to ponder:**

- Looking in the resistance is multiplied by  $(\beta+1)$ ; looking back it is divided by $(\beta+1)$ .

6.012 Design Problem

- The voltage gains of the third-stage emitter followers ( $Q_{25}$  and  $Q_{26}$ ) will likely be very close to one, but that of the stage-four followers might be noticeably less than one.

6.012 Design Problem

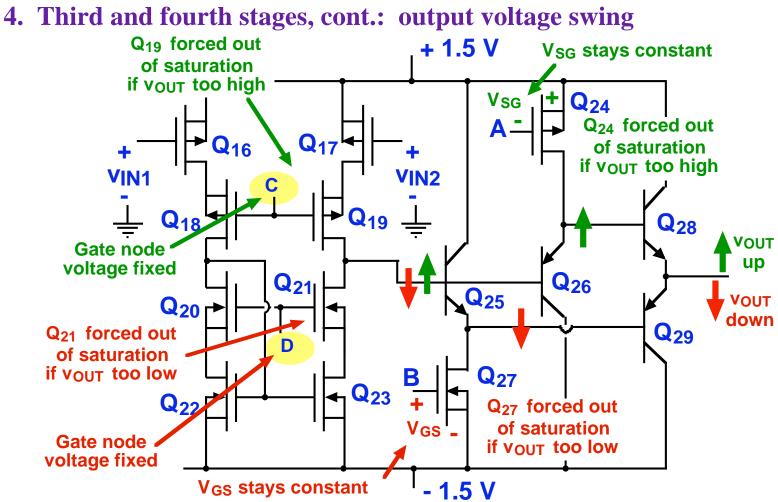

#### **Points to ponder:**

- How far + and can the node connecting the drains of  $Q_{19}$  and  $Q_{21}$  swing?

- How low can the voltage on the drain of  $Q_{27}$  go? How high for the drain of  $Q_{24}$ ? How much do  $v_{BE28}$  and  $v_{EB29}$  increase as  $|v_{OUT}|$  inceases?

6.012 Design Problem

4. Third and fourth stages: putting it all together

**Point to ponder:** - Now that I know everything, how can I meet the specs?

#### **Comments/Observations:**

- These stages involve four emitter follower building blocks arranged as two parallel cascades of two emitter follower stages each. These stages offer the most design challenges and tradeoffs of any of the stages in the design problem.

- They must be biased properly taking into account KVL and KCL constraints.

- Although they have voltage gains of almost one, these stages have a big effect on the overall voltage gain of the amplifier because they load the second gain stage.

- These stages determine the output resistance of the amplifier.

-  $I_{BIAS3}$  and  $I_{BIAS4}$  set the bias levels of  $Q_{25}$  and  $Q_{26}$ . The bias levels of  $Q_{28}$  and  $Q_{29}$  are set by the  $\gamma$ 's.

- A reasonable choice is to make  $\gamma_{28} = \gamma_{29}$ , and  $\gamma_{25} = [(\beta_n + 1)/(\beta_p + 1)]\gamma_{26}$ , in which case:

$$I_{E28}/I_{E25} = \gamma_{28}/\gamma_{25}$$

6.012 Design Problem

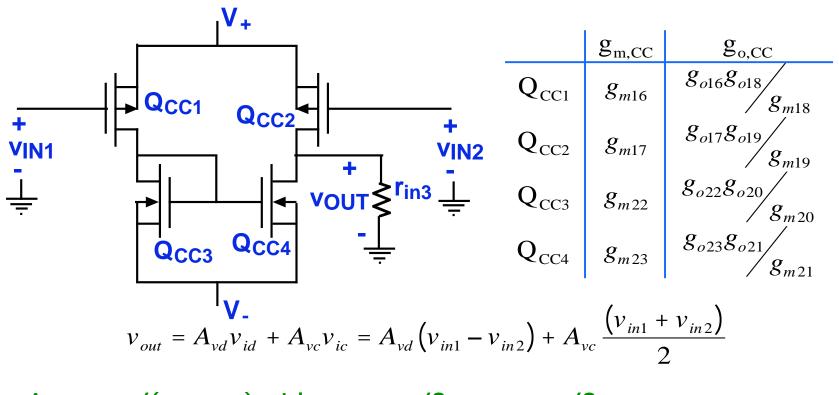

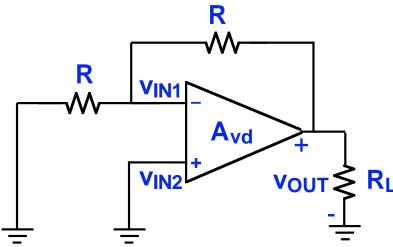

6. Overall gain expression

The defining relationships:

$$v_{out} = A_{vd}v_{id} + A_{vc}v_{ic} = A_{vd}(v_{in1} - v_{in2}) + A_{vc}(v_{in1} + v_{in2})/2$$

The difference-mode gain:

$$A_{vd} = A_{vd1} \cdot A_{vd2} \cdot A_{v3} \cdot A_{v4}$$

=  $\frac{-g_{m13}}{2(g_{013} + 2g_{o9})} \cdot \frac{-2g_{m17}}{\left(\frac{g_{017}g_{019}}{g_{m19}}\right) + \left(\frac{g_{023}g_{021}}{g_{m23}}\right) + g_{in3}} \cdot 1 \cdot \frac{(\beta_n + 1)2r_l}{r_{\pi 28} + (\beta_n + 1)2r_l}$

$r_l = 100\Omega$

The common-mode gain:

$$A_{vc} = A_{vc1} \cdot A_{vc2} \cdot A_{v3} \cdot A_{v4} = \frac{-g_{015}}{4g_{m9}} \cdot \frac{-1}{2} \cdot 1 \cdot \frac{(\beta_n + 1)2r_l}{r_{\pi 28} + (\beta_n + 1)2r_l}$$

#### **Point to ponder:**

- The follower stages treat the difference and common mode outputs the same.

- Let's put it all together and see what your design can do!

6.012 Design Problem

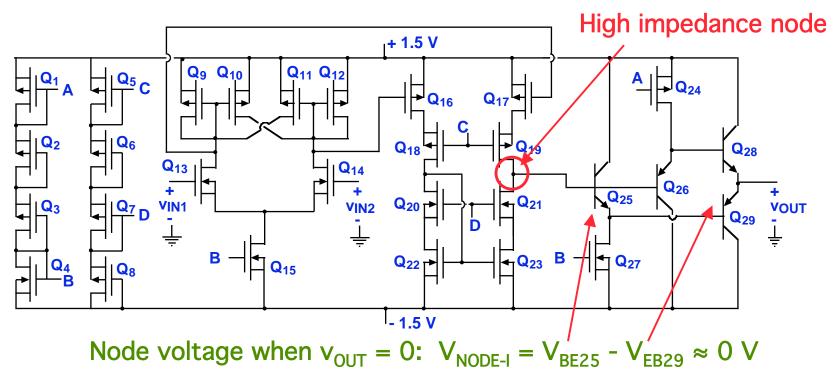

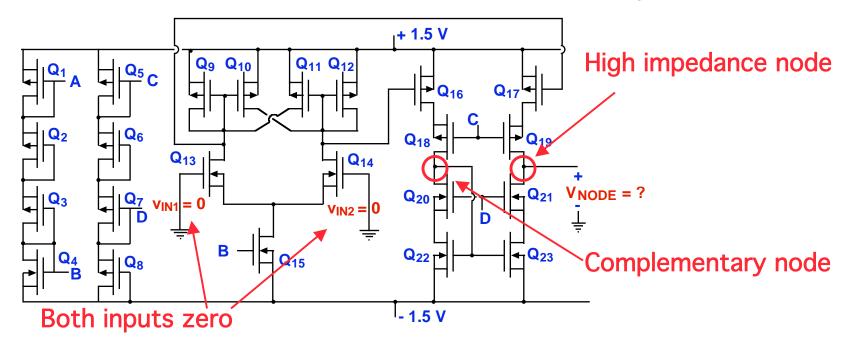

5. DC offset of a differential amplifier (OP-amp)

## Procedure for finding the DC offset:

I. Identify the high impedance node\* in the amplifier, and calculate what the voltage on that node is when the output voltage is zero.

\* Example: The output node of a CMOS inverter is an high impedance node. When both MOSFETs were saturated the voltage on this node could take on a range of values, and we couldn't say what  $v_{OUT}$  was when  $v_{IN}$  was  $V_{DD}/2$ .

6.012 Design Problem

**5.** DC offset of a differential amplifier (OP-amp)

## Procedure for finding the DC offset:

II. Disconnect the circuit following the high impedance node and calculate the voltage on the node when  $v_{IN1} = v_{IN2} = 0$ , assuming perfect symmetry and matching. Call this voltage  $V_{NODE-II}$ .

With perfect matching and symmetry,the voltage on the high impedance node will equal that on the complementary node. In this case  $V_{\text{NODE-II}}$  = -1.5V +  $V_{\text{GS22}}$

5. DC offset of a differential amplifier (OP-Amp)

# Procedure for finding the DC offset:

III. Knowing the differential voltage gain of the stage, Avd, we can calculate the DC off-set at the output by subtracting the voltage calculated in Step I, which we can call  $V_{NODE-I}$ , from the voltage calculated in Step II,  $V_{NODE-II}$ .

When  $v_{IN1} - v_{IN2} = (V_{NODE-I} - V_{NODE-II})/A_{vd}$ ,  $V_{OUT}$  is on the same order and thus essentially zero. We will define this value of  $v_{IN1} - v_{IN2}$  to be the DC offset, certainly compared to  $(V_{NODE-I} - V_{NODE-II})$ .

$DC offset = (V_{NODE-I} - V_{NODE-II})/A_{vd}$

$\begin{array}{c} \textbf{R}_{L} \end{array} \begin{array}{c} \textbf{Example: In the design problem,} \\ \text{if } A_{vd}. \text{turns out to be -1 x 10^4,} \\ \text{and } (V_{NODE-I} - V_{NODE-II}) \text{ is -0.9V,} \\ \text{then the DC offset is 90 } \mu \text{V.} \end{array} \end{array}$

6.012 Design Problem

6.012 Microelectronic Devices and Circuits Fall 2009

For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.