#### 6.012 - Microelectronic Devices and Circuits

# Lecture 14 - Digital Circuits: Inverter Basics - Outline

- Announcements

- **Stellar Two supplemental readings posted Exam Two - Be the first in your living unit to study for it.**

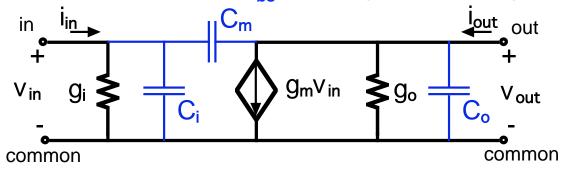

### • Review - Linear Equivalent Circuits Everything depends on the bias; only low frequency for now

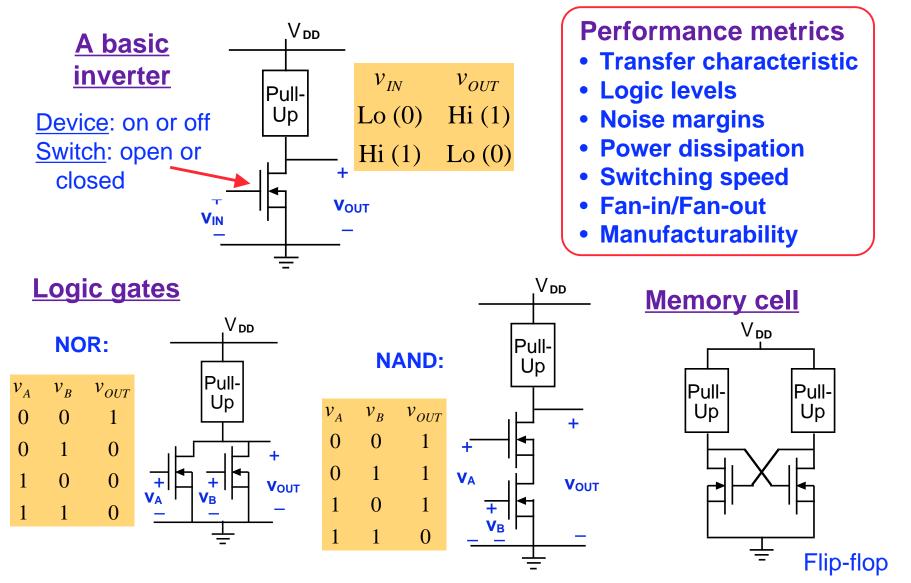

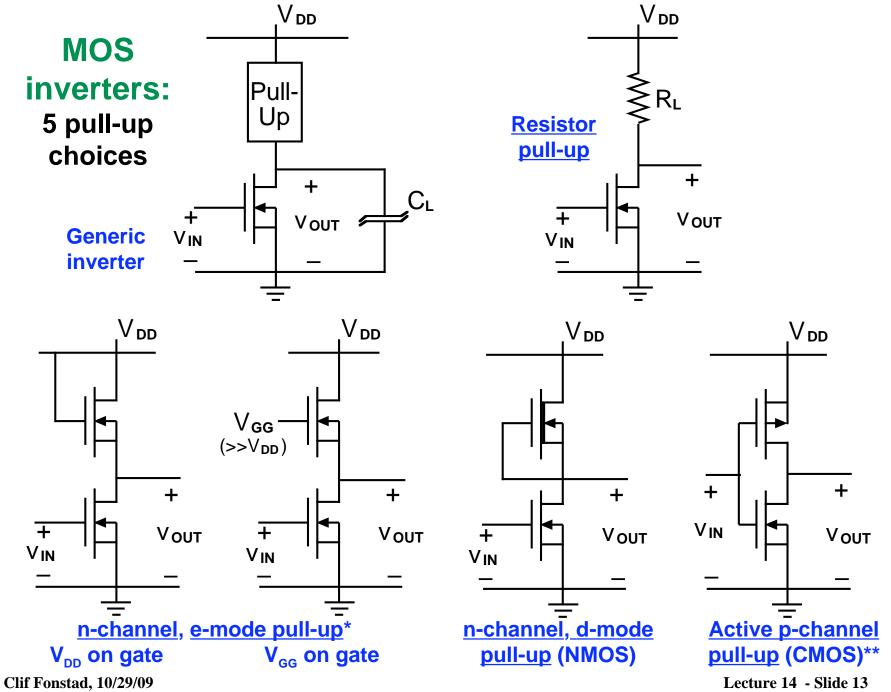

# • Digital building blocks - inverters

A generic inverter MOS inverter options

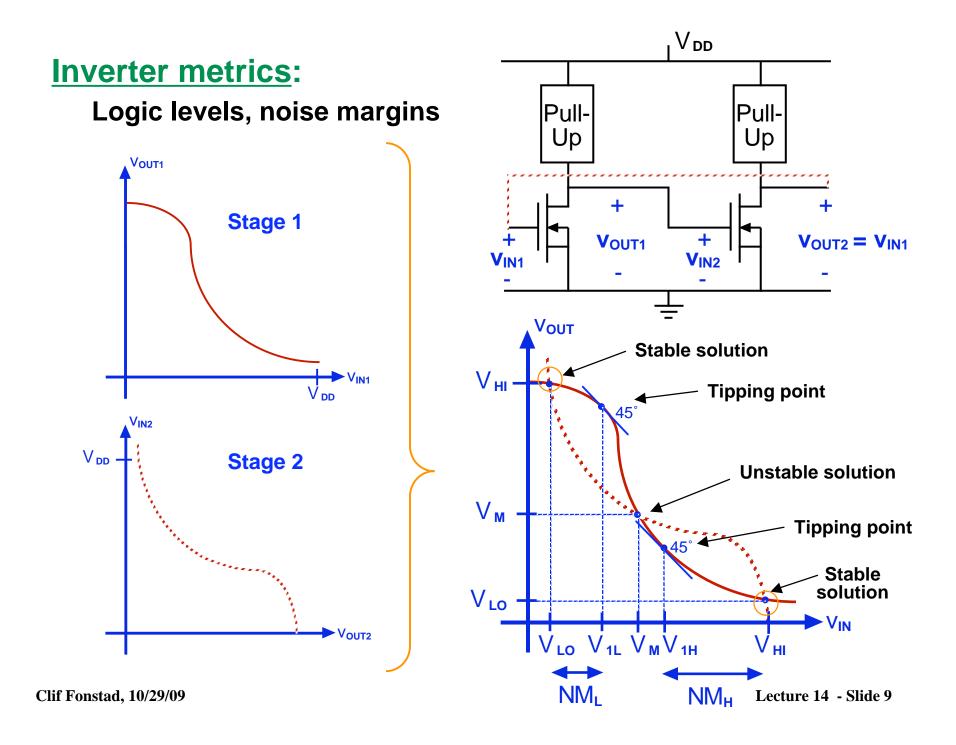

# • Digital inverter performance metrics

Transfer characteristic: logic levels and noise margins Power dissipation Switching speed Fan-out, fan-in Manufacturability

# • Comparing the MOS options And the winner is....

### **Reviewing our LECs:** Important points made in Lec. 14

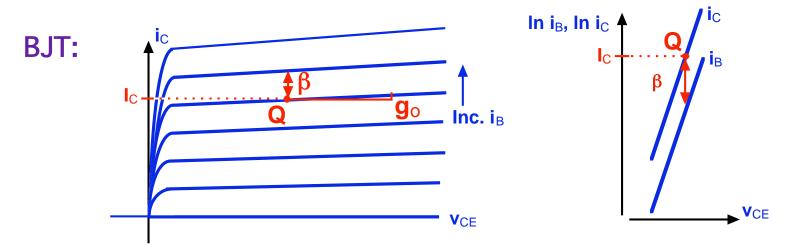

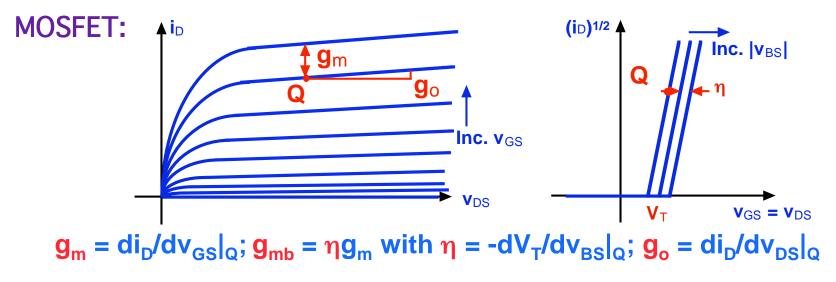

We found LECs for BJTs and MOSFETs in both strong inversion and sub-threshold. When  $v_{bs} = 0$ , they all look very similar:

Most linear circuits are designed to operate at frequencies where the capacitors look like open circuits. We can thus do our designs neglecting them.\*

| Bias dependences:            | BJT                  | ST MOS                             | SI MOS                   |                       |

|------------------------------|----------------------|------------------------------------|--------------------------|-----------------------|

| $g_i$ :                      | $q I_C / \beta_F kT$ | 0                                  | 0                        |                       |

| $g_m$ :                      | q I <sub>c</sub> /kT | q <mark>I<sub>D</sub>/</mark> n kT | $\sqrt{2K_o I_D/\alpha}$ | ST = sub-threshold    |

| $g_{\scriptscriptstyle o}$ : | $\lambda I_{C}$      | $\lambda I_D$                      | $\lambda I_D$            | SI = strong inversion |

The LEC elements all depend on the bias levels. Establishing a known, stable bias point is a key part of linear circuit design. We use our large signal models in this design and analysis.

Clif Fonstad, 10/29/09

\* Only when we want to determine the maximum frequency to which our designs can usefully operate must we include the capacitors.

#### **LECs:** Identifying the incremental parameters in the characteristics

$g_m = ql_C/kT; g_\pi = \beta g_m \text{ with } \beta = di_C/di_B|_Q; g_o = di_C/dv_{CE}|_Q$

Clif Fonstad, 10/29/09

### **Building Blocks for Digital Circuits: inverters**

Clif Fonstad, 10/29/09

Lecture 14 - Slide 4

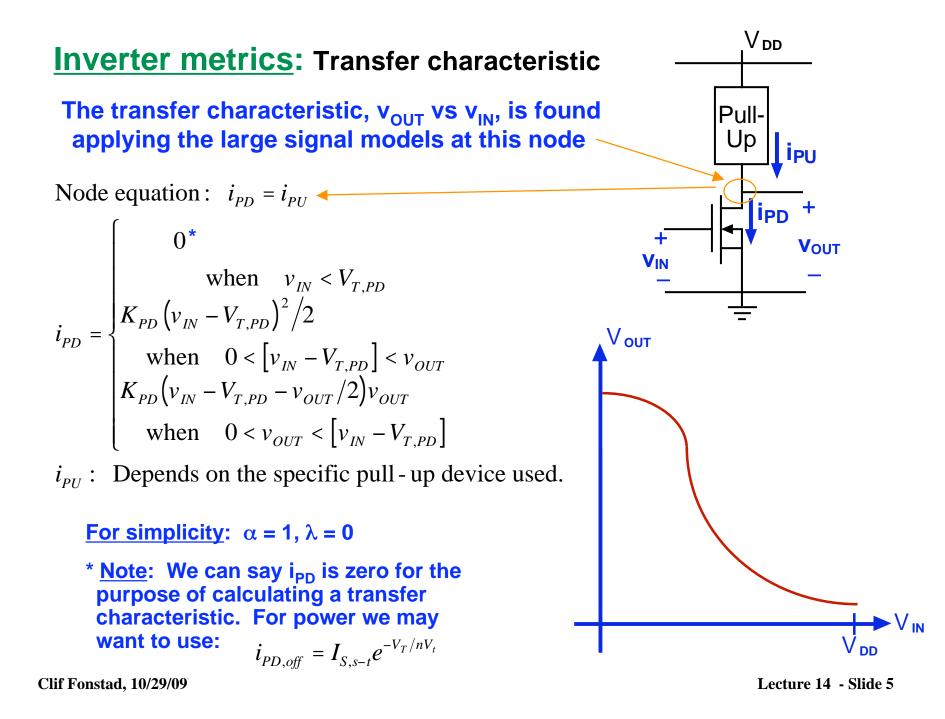

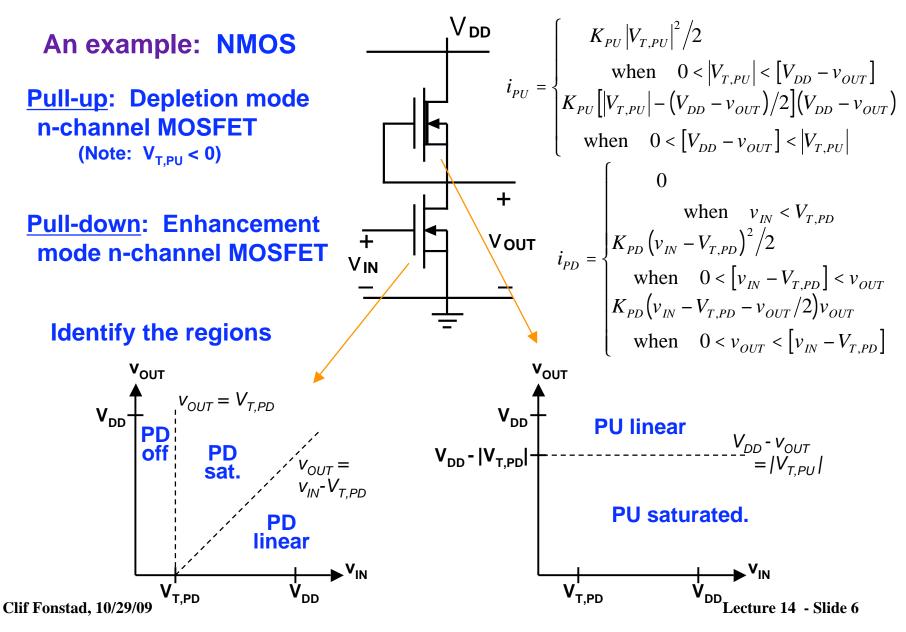

#### **Inverter metrics:** Transfer characteristic, cont.

#### **Inverter metrics:** Transfer characteristic, cont.

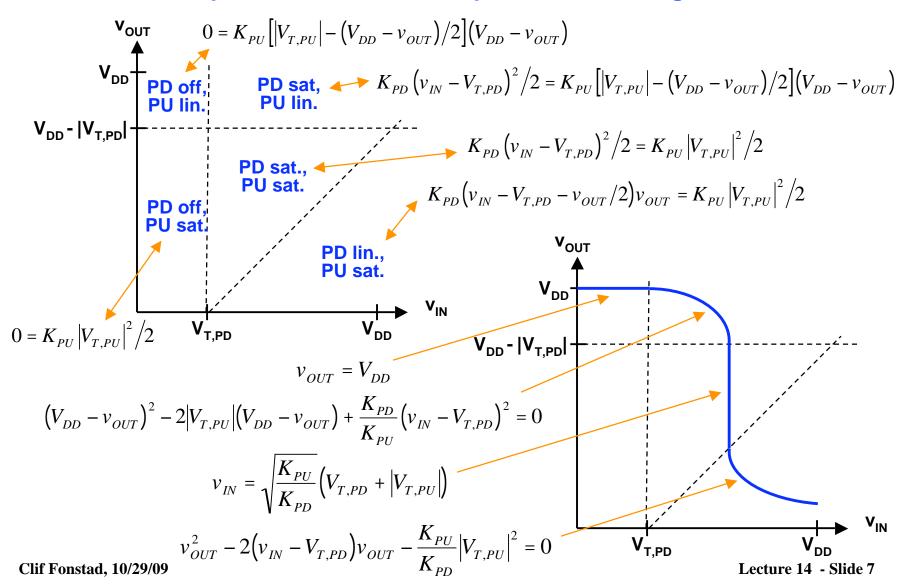

Combine the plots; write the node equation in each region and solve.

### **Inverter metrics:** Transfer characteristic, cont.

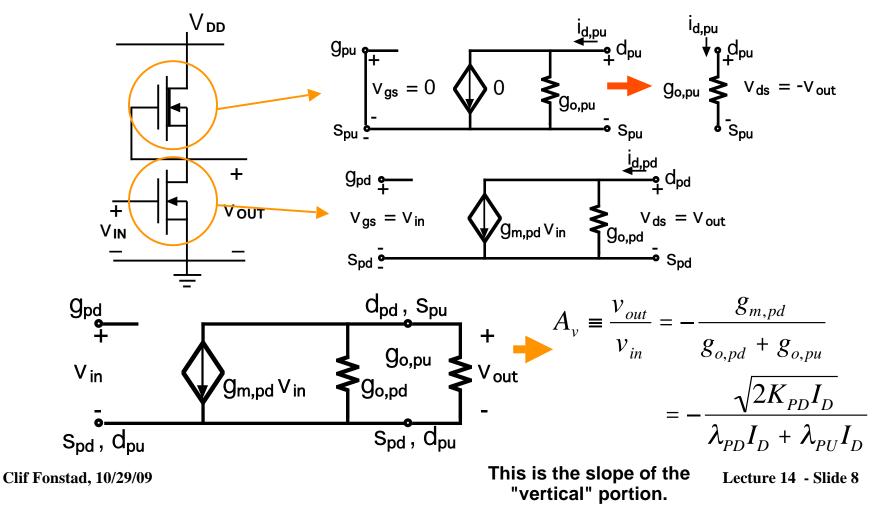

Is the characteristic really vertical and  $v_{OUT}$  indeterminate when both transistors are in saturation? It is if  $\lambda = 0$  (i.e. no Early effect), but we know this isn't true. We can find the slope when  $\lambda \neq 0$  from an LEC analysis about the bias point  $v_{OUT} = v_{IN} = \sqrt{K_{PU}/K_{PD}} \left(V_{T,PD} + |V_{T,PU}|\right)$ .

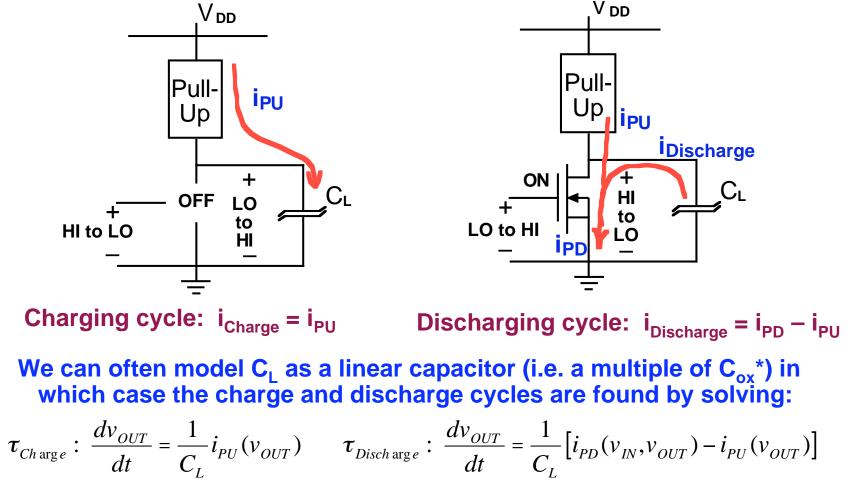

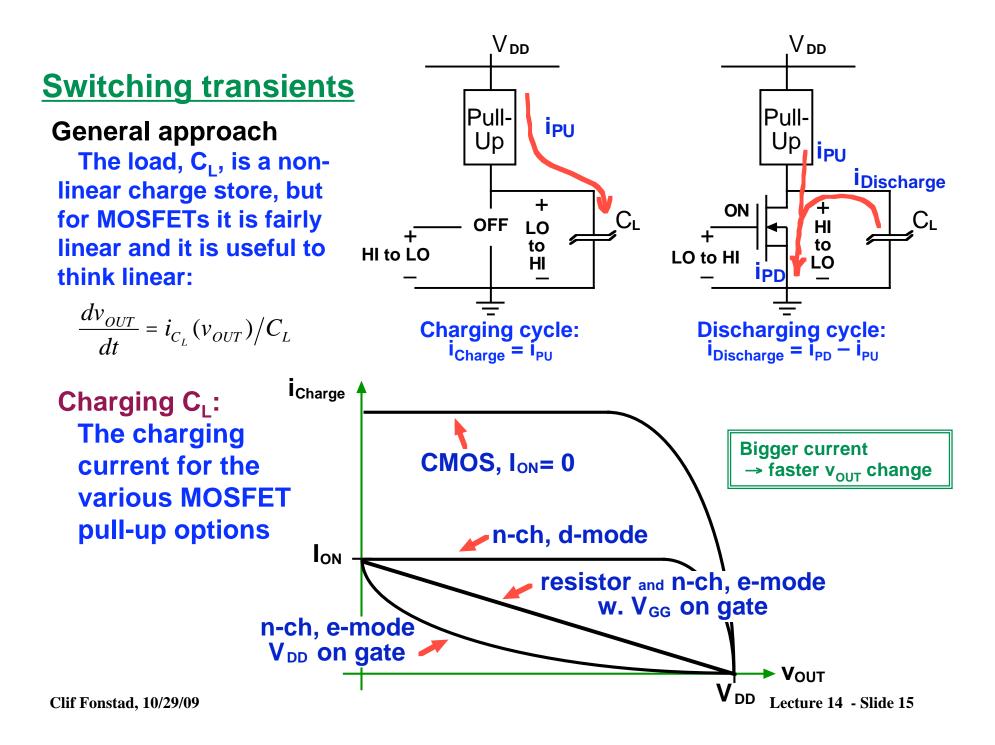

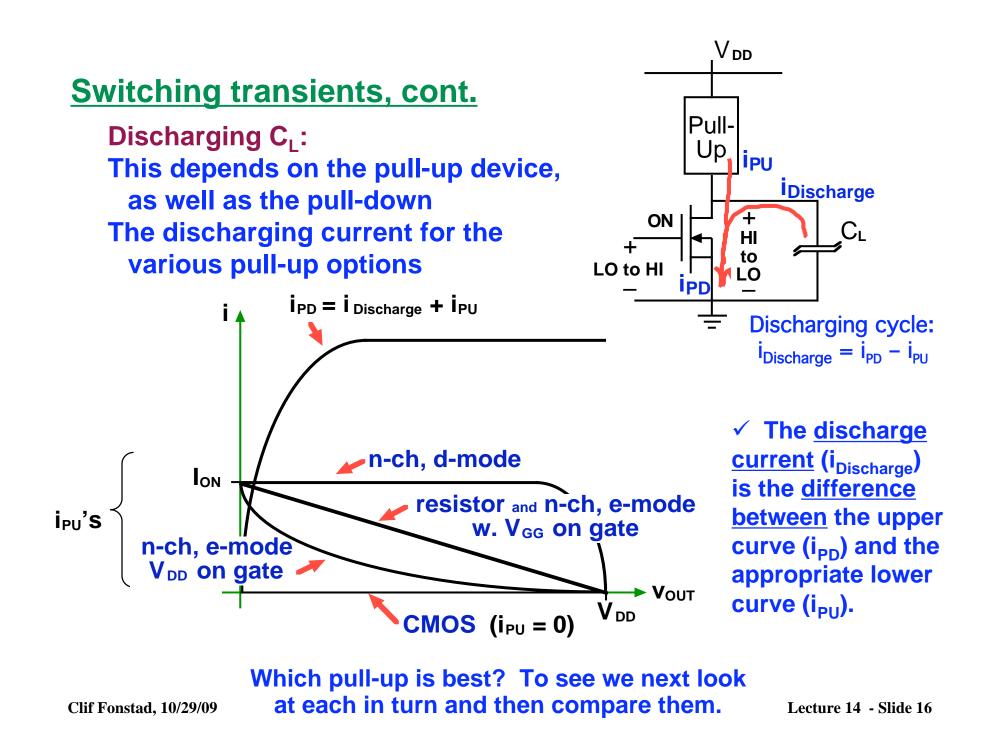

### **Inverter metrics:** Switching times (gate delay)

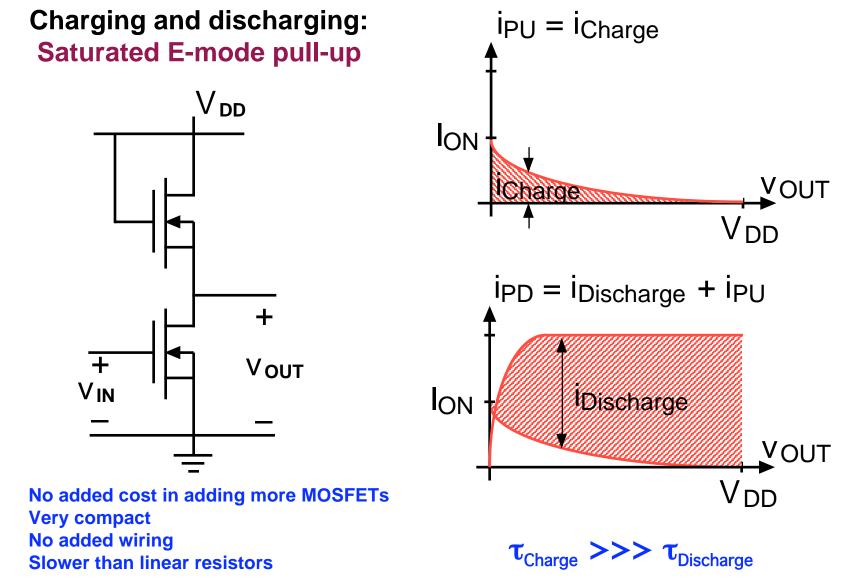

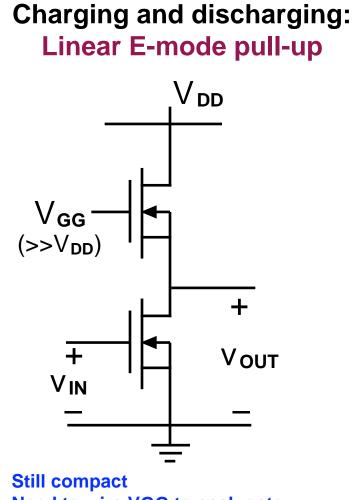

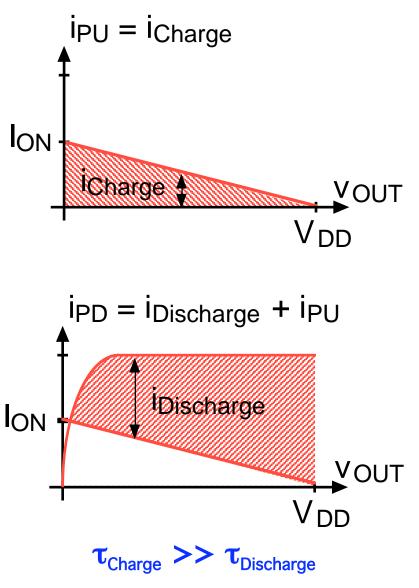

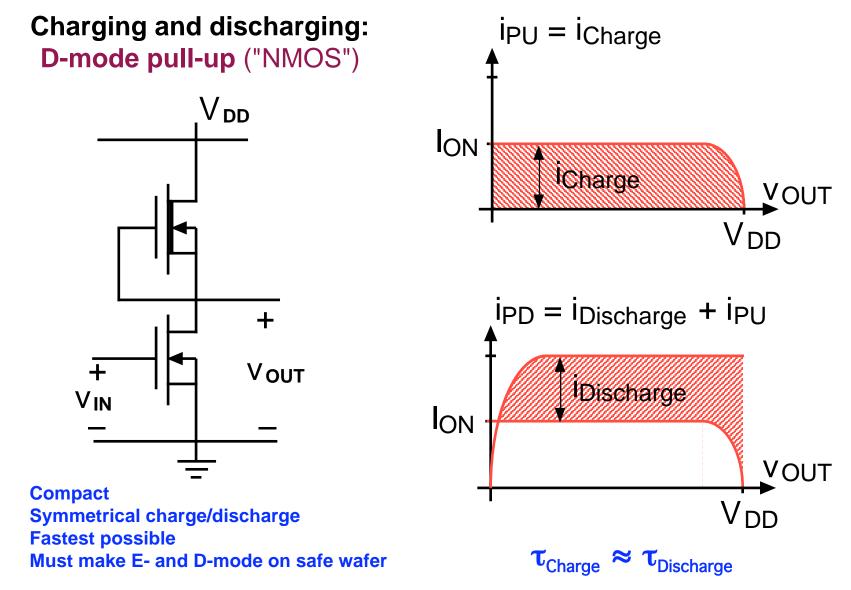

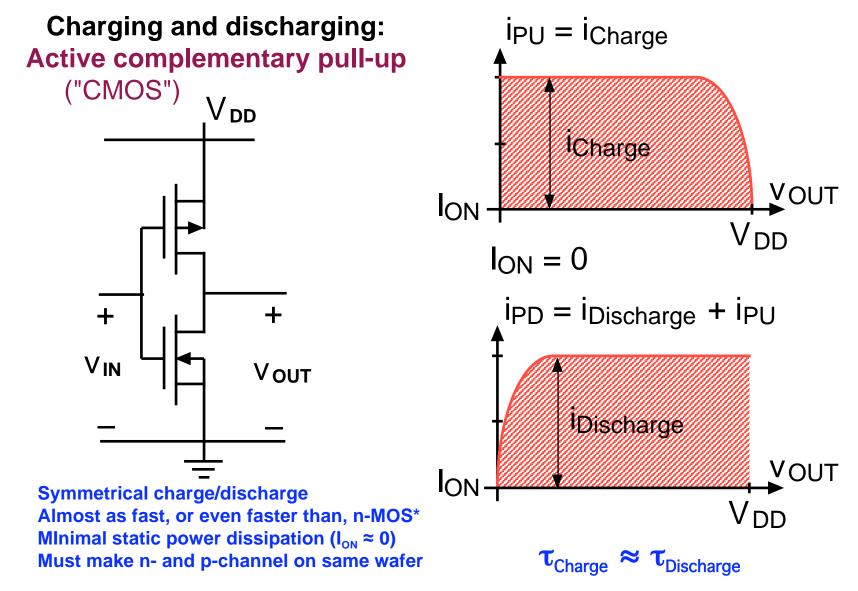

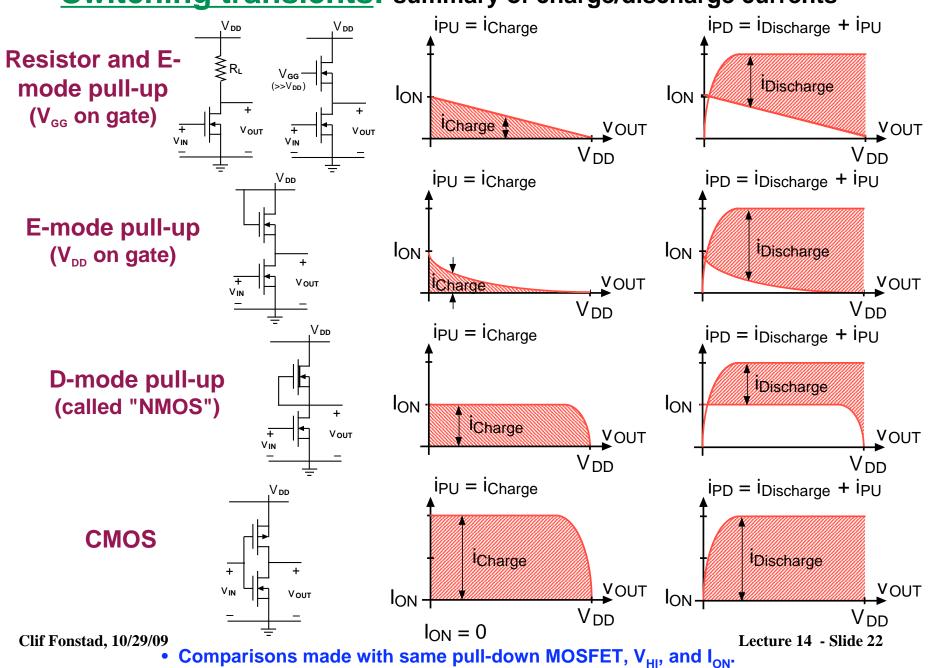

When the output goes from LO to HI, the load charge store must be charged through the pull-up device. When the output goes from HI to LO, it is discharged through the pull-down device.

**Clif Fonstad, 10/29/09**

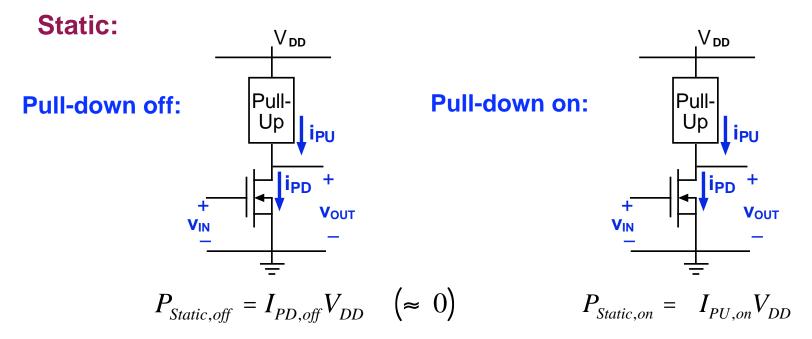

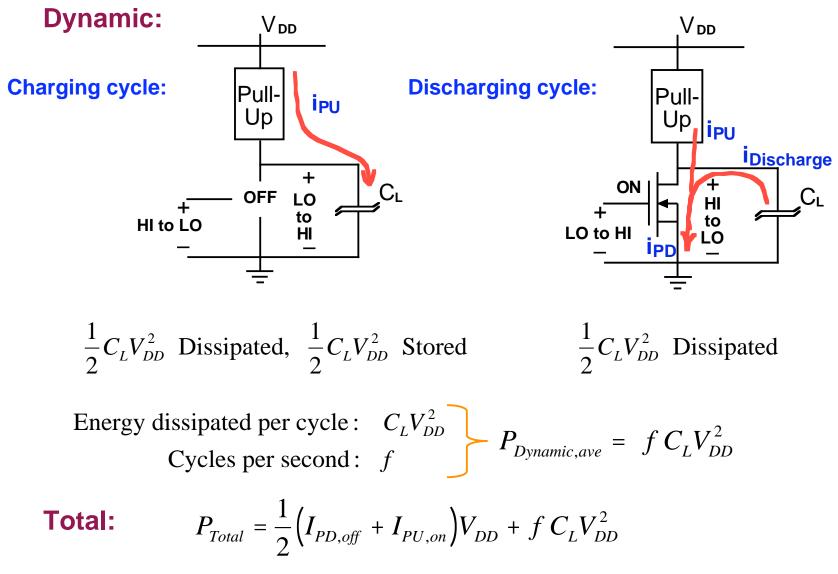

### **Inverter metrics:** Power

**Total Power:**

Two components - static and dynamic (switching)

$$P_{Total} = P_{Static} + P_{Dynamic}$$

To estimate the total static power we assume the typical pull-down is off half the time and on half the time.

$$P_{Static,ave} = \frac{1}{2} P_{Static,on} + \frac{1}{2} P_{Static,off} = \frac{1}{2} \left( I_{PD,off} + I_{PU,on} \right) V_{DD}$$

**Clif Fonstad, 10/29/09**

### Inverter metrics: Power, cont.

Clif Fonstad, 10/29/09

\* Called PMOS when made with p-channel FETs.

\*\* Notice that CMOS has a larger (~3x) input capacitance.

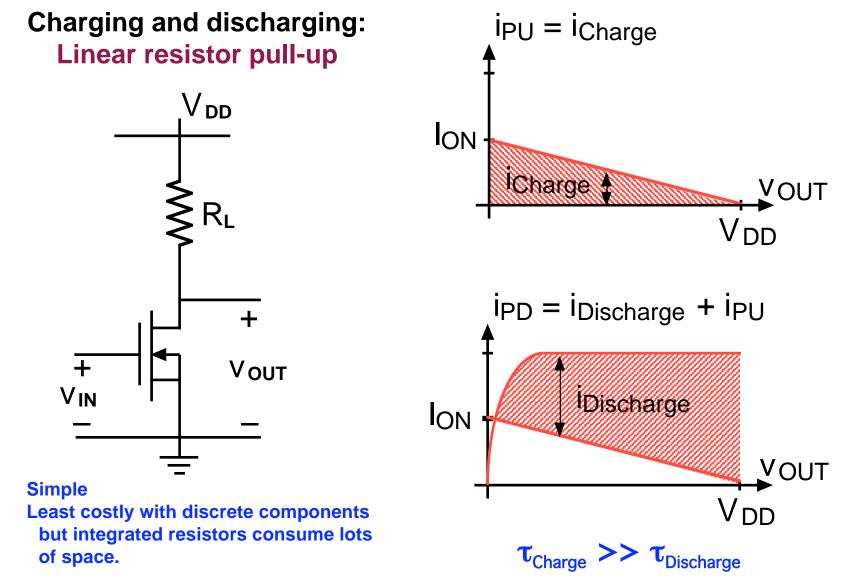

### **MOS inverters:** Comparing the 5 pull-up choices

**Ground rules:**

To make the comparison meaningful, we set the following conditions:

1. We use the <u>same pull-down</u> device with each of the different pull-ups.

2. We use the <u>same fan out</u>, n, to identical inverters to have a valid comparison of the amount of charge that must managed to charge and discharge, and of the dynamic power dissipation. We also assume the load capacitance,  $C_L$ , is linear and n times a single inverter input capacitance.

3. We use the same  $V_{HI}$  and  $I_{PU,on}$  so the static power dissipation is the same.

In this way we can see which pull-up gives us the highest speed, all else being equal.

Clif Fonstad, 10/29/09

**Clif Fonstad, 10/29/09**

Need to wire VGG to each gate Need second supply Not faster than linear resistor

Clif Fonstad, 10/29/09

Clif Fonstad, 10/29/09

Clif Fonstad, 10/29/09 \* The input capacitance is 3x larger, but the interconnect capacitance Lecture 14 - Slide 21 is the same, so it depends on which of the two is dominant.

### Switching transients: summary of charge/discharge currents

# **MOS Technology**: An abbreviated history

p-MOS:

In the beginning (mid-60s) there were only metal-gate p-channel emode MOSFETs; n-channel MOSFETs came out d-mode. p-MOS logic relied on saturated and linear e-mode pull-ups.

n-MOS:

With the development of <100> substrates, e-beam deposition, selfaligned poly-Si gates, and ion implantation, initially to improve p-MOS, it became possible to also reliably fabricate e-mode n-channel FETs. NMOS, with d-mode pull-ups, then took off (ca 1970).

### CMOS:

- It was clear for many years that CMOS inverters were superior, but fabricating them reliably in high density and at low cost was a big challenge. Eventually manufacturers learned how to make n- and p-channel MOSFETS together in close proximity and economically (ca 1980); CMOS then soon became the dominant IC technology because of its superior low power and high speed.

- For the past decade the industry has been fixated on systematically making FETs smaller, circuits more dense, and wafers larger.\*

Clif Fonstad, 10/29/09 \* And with good reason; more next week in Lecture 17. Lecture 14 - Slide 23

6.012 - Microelectronic Devices and Circuits

# Lecture 14 - Digital Circuits: Inverter Basics - Summary

• Digital building blocks - inverters

A generic inverter: Switch = pull-down device, Load = pull-up device MOS inverter options - Pull-down: n-channel, e-mode (faster than p-channel) Pull-up: 1. resistor; 2. n-channel, e-mode w. and w.o. gate bias; 3. n-channel, d-mode (NMOS); 4. p-channel, e-mode (CMOS)

### • Digital inverter performance metrics

**Transfer characteristic**

**Logic levels:**  $V_{HI}$ ,  $V_{LO}$ **Noise margins:**  $NM_{HI}$  (high), and  $NM_{LO}$  (low) **Design variables:** choice of pull-up device

pull-up and pull-down thresholds device sizes (absolute and relative)

**Power dissipation:** stand-by power and switching dissipation **Switching speed:** capacitive load

charge and discharge currents critical

**Fan-out, fan-in:** minimal issue in MOS; more so with BJT logic **Manufacturability:** small, fast, low-power, reliable, and cheap

### • Comparing the MOS options And the winner is....CMOS

6.012 Microelectronic Devices and Circuits Fall 2009

For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.