6.012 - Microelectronic Devices and Circuits

# Lecture 25 - Beyond Si; Beyond 6.012 - Outline

## Announcements

HKN Evaluation - Do before final so you're still in a good mood.

Final - Tuesday, Dec 15, 9:00 am to Noon Covering all the course; closed book; 4 problems

# • Sub-threshold Circuit - What, Why, How

**Applications:** medical implants, remote sensors, portable devices **Digital design:** choosing V<sub>DD</sub> for minimum energy per operation

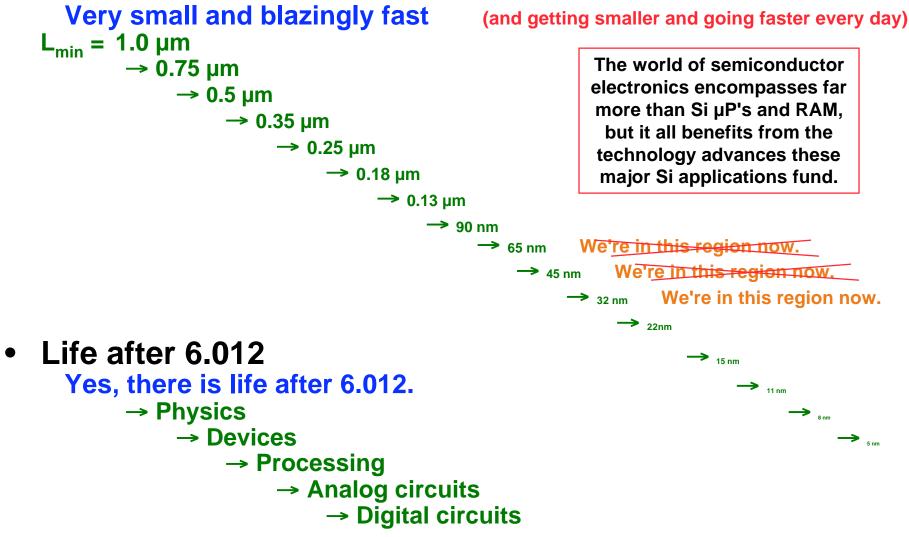

## • **Devices we have known** - Where are they now:

MOSFETs: 5 nm Si, III-V high electron mobility transistors BJTs: InP based double heterojunction bipolar transistors LEDs: white lighting; laser diodes Solar cells: multi-junction, multi-material concentrator cells

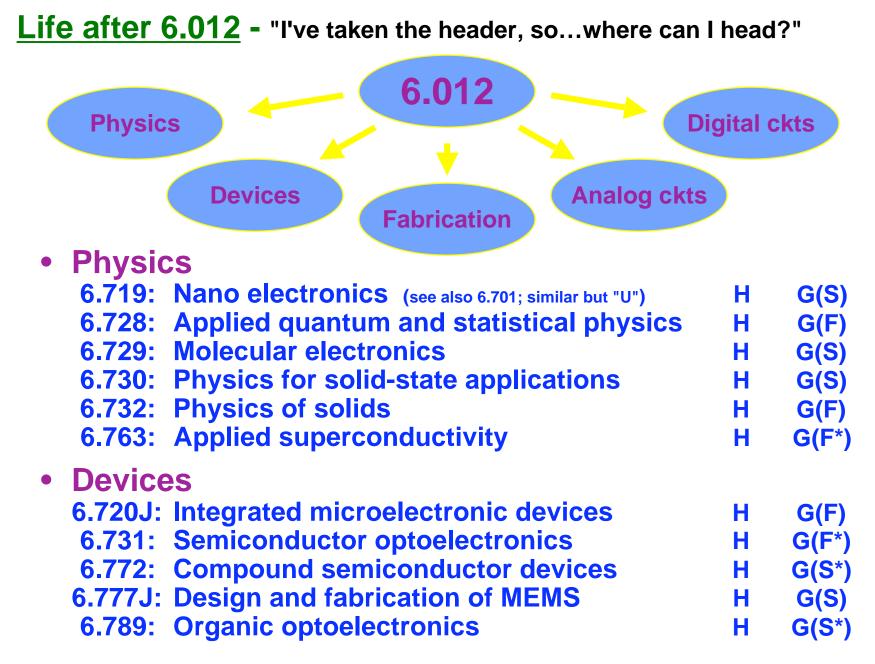

# • Life after 6.012

Is it possible? ("Where does one head after taking the header?")

# Sub-threshold Circuit Design: The need for low energy

Emerging applications require ultra-low energy:

μ-sensors, medical devices

Images removed due to copyright restrictions: cartoons and figures illustrating microsensors, medical devices, ambient intelligence, and portable devices.

Ambient intelligence, portable devices

Sub-threshold operation: Slow, lower power, minimum energy operation becomes possible

Sub-V<sub>T</sub> benefits: Power Energy

Concerns: Increased sensitivity to noise and to variations in  $V_T$  and T.

**Clif Fonstad**, 12/10/09

Research at M.I.T. under Prof. Anantha Chandrakasan.

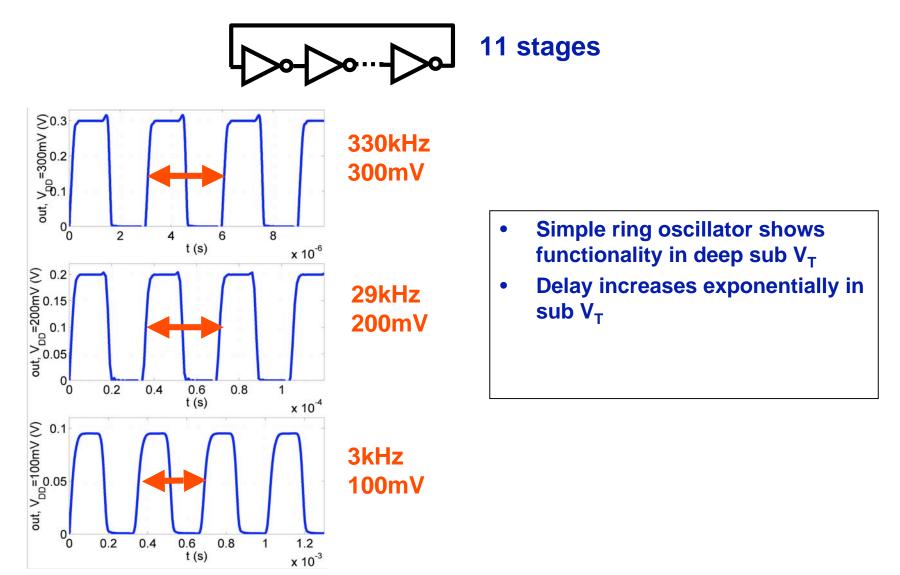

## Sub-threshold Circuit Design: Digital Inverters, cont.

Clif Fonstad, 12/10/09

# Work of Benton H. Calhoun at M.I.T. under Prof. Anantha Chandrakasan's supervision.

Lecture 25 - Slide 3

Courtesy of Benton Calhoun and Anantha Chandrakasan. Used with permission.

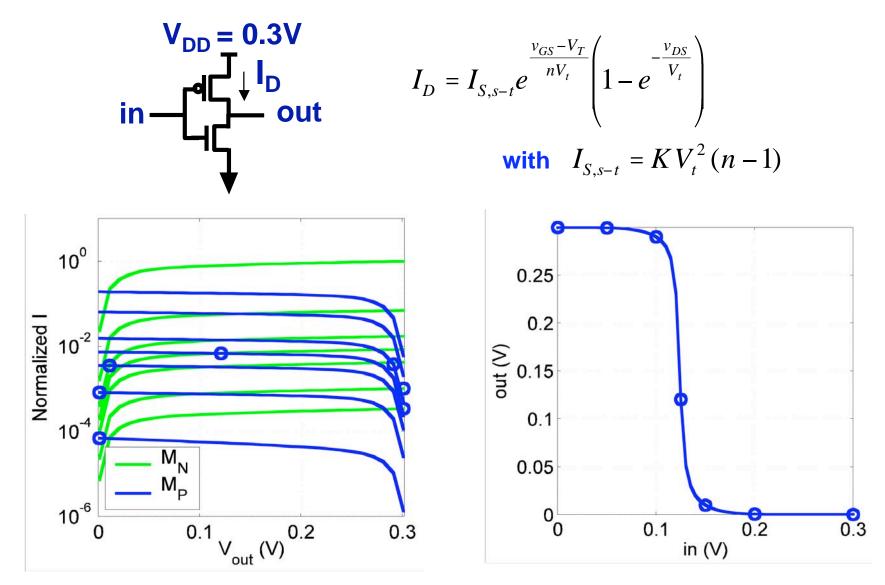

# Sub-threshold Circuit Design: Digital Inverters

**Operation of standard CMOS gate with V\_{DD} < V\_{T}**

Clif Fonstad, 12/10/09

# Work of Benton H. Calhoun at M.I.T. under Prof. Anantha Chandrakasan's supervision.

Lecture 25 - Slide 4

Courtesy of Benton Calhoun and Anantha Chandrakasan. Used with permission.

## Sub-threshold Circuit Design: CMOS Inverters, cont.

In low-power applications an important metric the energy per operation,  $E_{pop}$ . There is an optimum supply voltage that minimizes  $E_{pop}$ .

Operating in strong inversion,  $E_{pop} = C_L V_{DD}^2$ , and reducing  $V_{DD}$  clearly reduces  $E_{pop}$ . As  $V_{DD}$  approaches  $V_T$ , however, the contribution of subthreshold leakage becomes important, especially because the gate delay,  $\tau_{GD}$  (time per operation) increases as charging current decreases.

#### In general:

$$\tau_{GD} = 2C_L V_{DD} / I_{D,sat}$$

Only  $I_{D,sat}$  is different depending on the region of operation.

In strong inversion:

$$I_{D,sat} = K (V_{DD} - V_T)^2 / 2$$

Sub-threshold:

$$I_{D,sat} = K V_t^2 (n-1) e^{(V_{DD} - V_T)/nV_t}$$

Just above threshold:

$$I_{D,sat} = K \left[ V_t^2 (n-1) + \left( V_{DD} - V_T \right)^2 / 2 \right]$$

Thanks to Naveen Verma for discussions on sub-threshold circuits.

Clif Fonstad, 12/10/09

### Sub-threshold Circuit Design: CMOS Inverters, cont.

The energy per operation,  $E_{pop}$ , including energy dissipated by the subthreshold leakage current,  $I_{leakage} \times \tau_{GD} \times \#$  of idle gates is:

$$E_{pop} = C_L V_{DD}^2 + A I_{leakage} V_{DD} \tau_{GD} = C_L V_{DD}^2 \left[ 1 + 2A I_{leakage} / I_{D,sat} \right]$$

A is the average number of idle gates per active gate, and the leakage current is:  $I_{leakage} = KV_t^2(n-1)e^{-V_T/nV_t}$

Evaluating  $E_{pop}$  in each region of operation we find:

$$E_{pop} = \begin{cases} C_L V_{DD}^2 \left[ 1 + 2A e^{-V_{DD}/nV_t} \right] & \text{Sub-threshold} \\ \\ C_L V_{DD}^2 \left[ 1 + \frac{2A e^{-V_{DD}/nV_t}}{1 + \left(V_{DD} - V_T\right)^2 / 2V_t^2 \left(n - 1\right)} \right] & \text{Just above threshold} \\ \\ C_L V_{DD}^2 & \text{In strong inversion} \end{cases}$$

#### These expressions are plotted on the next slide.

Thanks to Naveen Verma for discussions on sub-threshold circuits.

**Clif Fonstad**, 12/10/09

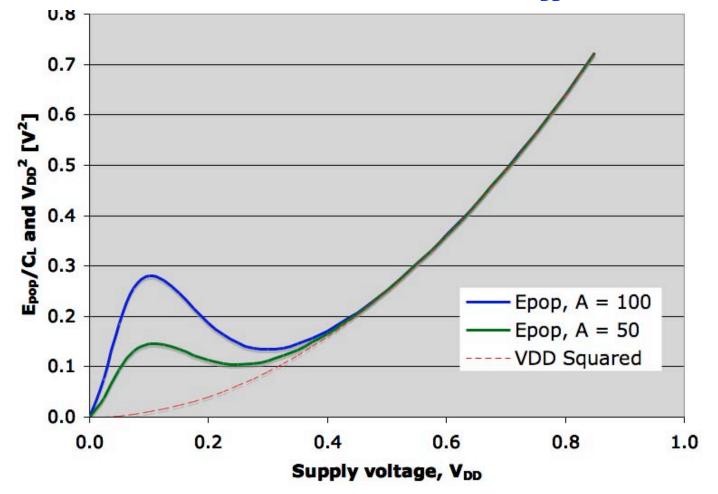

# Sub-threshold Circuit Design: Minimizing Energy per Operation in CMOS Logic

The energy per operation,  $E_{pop}$ , assuming  $|V_T| = 0.4 V$ , n = 2, and A = 50 and 100 is plotted below. Note the minimum for  $V_{DD}$  a bit below  $V_T^{**}$ :

\*\* The results are quite sensitive in detail to the values of n, A, and V<sub>T</sub>. Thanks to Naveen Verma for sub-threshold circuit discussions.

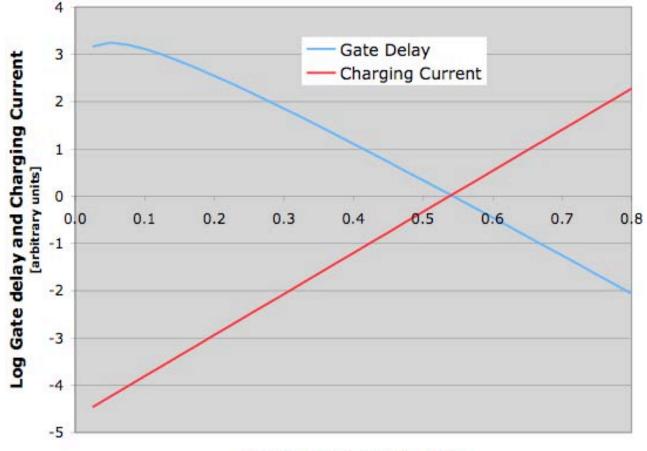

# Sub-threshold Circuit Design: Minimizing Energy per Operation, cont.

Reducing  $V_{DD}$  reduces the charging/discharging currents rapidly and increases the cycle time significantly, so  $E_{min}$  operation is low speed.

Supply Voltage, V<sub>DD</sub> [V]

#### For many remote and monitoring sensor application this is just fine.

Clif Fonstad, 12/10/09

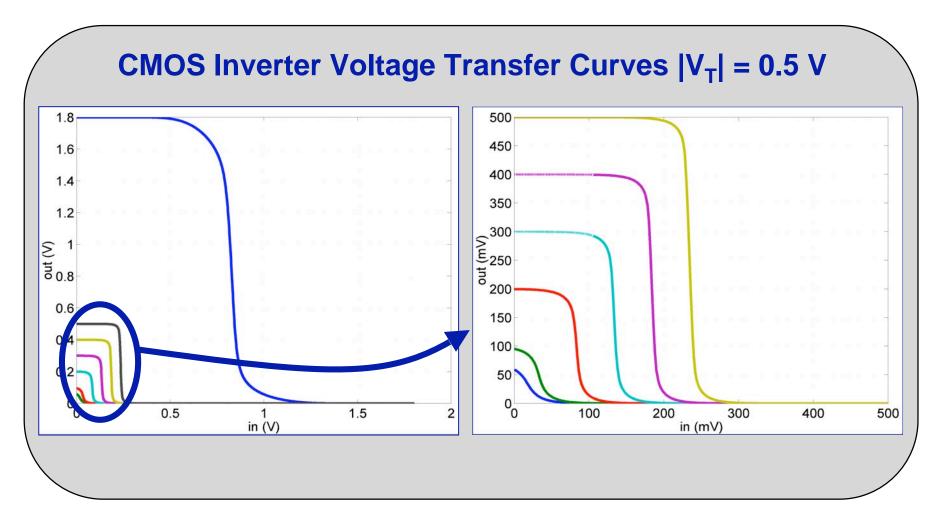

# Sub-threshold Circuit Design: CMOS Inverters, cont.

# Work of Benton H. Calhoun at M.I.T. under Prof. Anantha Chandrakasan's supervision.

Lecture 25 - Slide 9

Courtesy of Benton Calhoun and Anantha Chandrakasan. Used with permission.

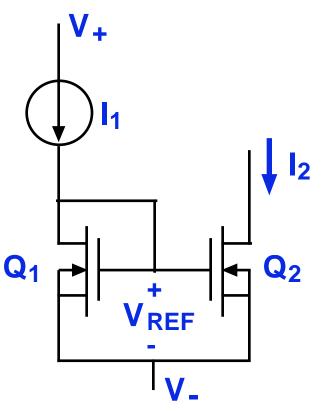

# **Sub-threshold Circuit Design:** Linear circuits

- Conventional stages and designs can be operated in subthreshold, just as was done with CMOS gates. They are slow, but if power is a concern and high speed isn't (i.e, under 10 MHz is OK), they are worth considering.

- New types of MOS circuits are also possible: Translinear circuits.\* Consider first, for example, the sub-threshold current mirror on the right:

$$V_{REF} - V_T = -n V_t \ln \frac{I_1}{W_1 I_{S,s-t}}$$

$$V_2 = W_2 I_{S,s-t} e^{-(V_{REF} - V_T)/nV_t} = \frac{W_2}{W_1} I_1$$

# Note the exp to *L*n and *L*n to exp conversions.

\* Translinear circuits were invented by Barrie Gilbert of Analog Devcies working with BJTs (IEEE JSSC, Vol SC-3, No. 4, Dec. 1968, pp. 353-373).

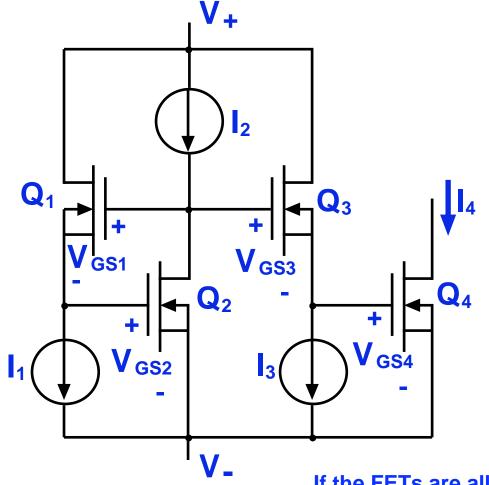

# Sub-threshold Circuit Design: Translinear circuits, cont.

Now consider using this log function and its inversion to do multiplication. Consider the following circuit:

To begin note that:

$$v_{GS1} + v_{GS2} = v_{GS3} + v_{GS4}$$

and:

$$v_{GSi} - V_T = -n V_t \ln \frac{I_i}{W_i I_{S,s-t}}$$

**Isolating v<sub>GS4</sub>:**

$$v_{GS4} = v_{GS1} + v_{GS2} - v_{GS3}$$

and substituting , we find:

$$I_4 = \frac{I_1 \cdot I_2}{I_3} \cdot \frac{W_3 \cdot W_4}{W_1 \cdot W_2}$$

Circuits like this can be used to do analog multiplication.

If the FETs are all the same width:

$$I_4 = \frac{I_1 \cdot I_2}{I_3}$$

\* After 6.376 notes via Naveen Verma.

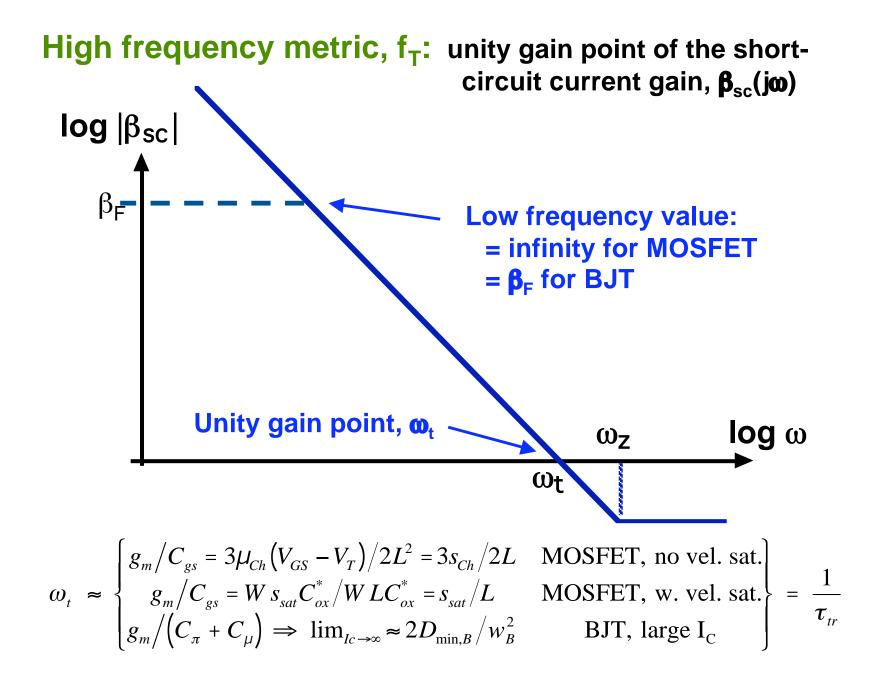

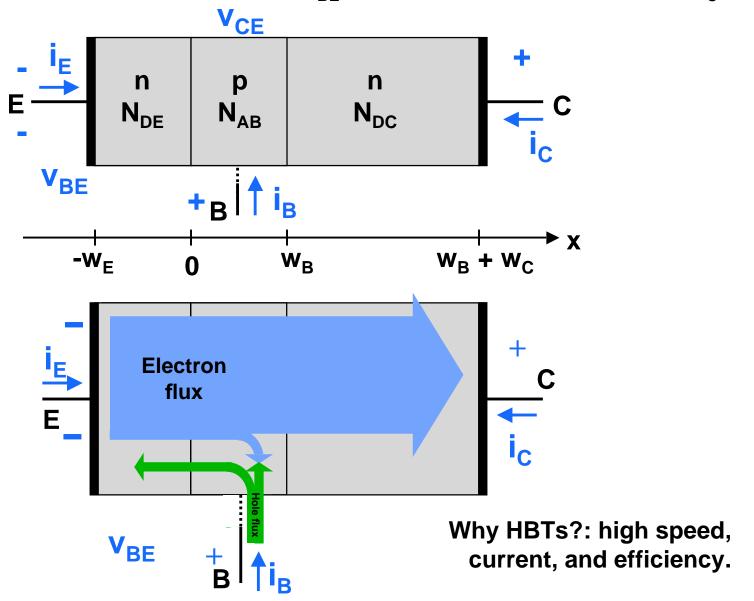

**<u>Bipolar Junction Transistors</u>**: basic operation and modeling...

... how the base-emitter voltage,  $v_{BE}$ , controls the collector current,  $i_{C}$

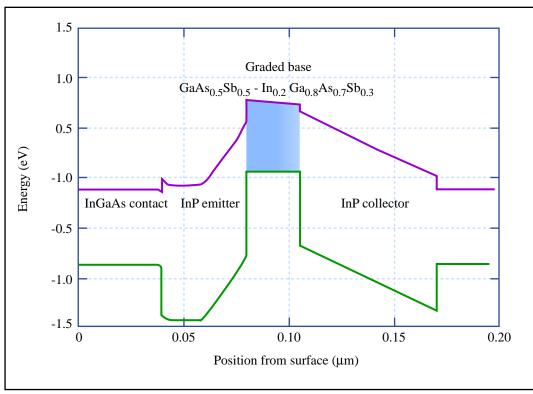

<u>Heterojunction BipolarTransistors</u>: higher mobility materials, graded base to create drift field, different  $E_g$  to tailor injection

Figure by MIT OpenCourseWare.

#### Work of Prof. Milton Feng and students at University of Illinois

Source: Compound Semiconductor, March 2008

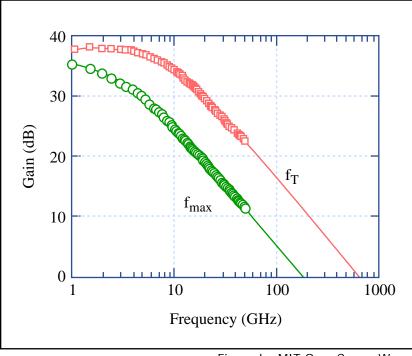

#### <u>Heterojunction BipolarTransistors, cont</u>: $f_T = 685$ GHz @ R.T.

Figure by MIT OpenCourseWare.

Notice that performance above 50-100 GHz is extrapolated using the theoretical frequency dependence to get  $f_T$  and  $f_{max}$  values. This is accepted practice because the instrumentation needed does not exist.

Source: Compound Semiconductor, March 2008

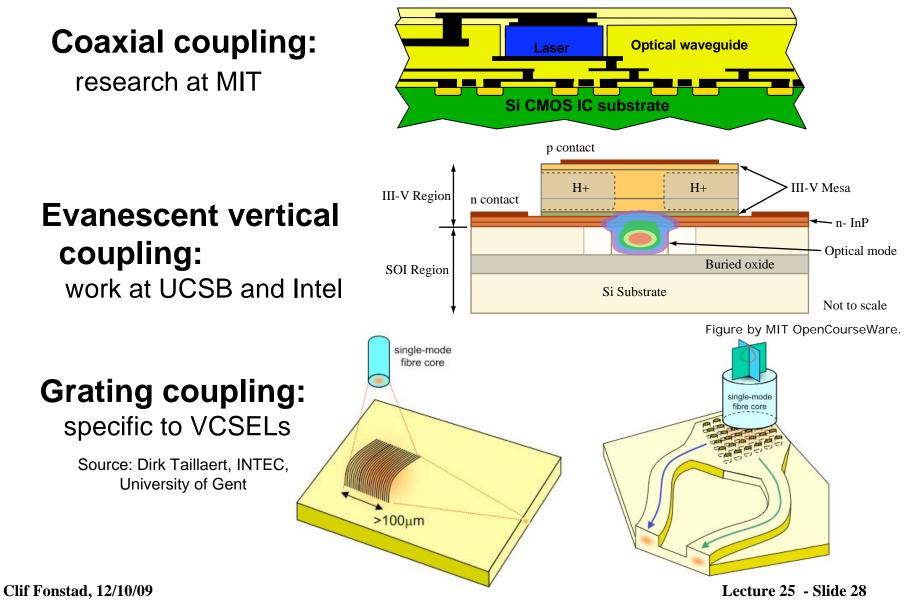

# Mixing technologies and materials on a Si platform: other routes to keeping performance on the Si roadmap; optoelectronic integration

Courtesy of Dirk Taillaert. Used with permission.

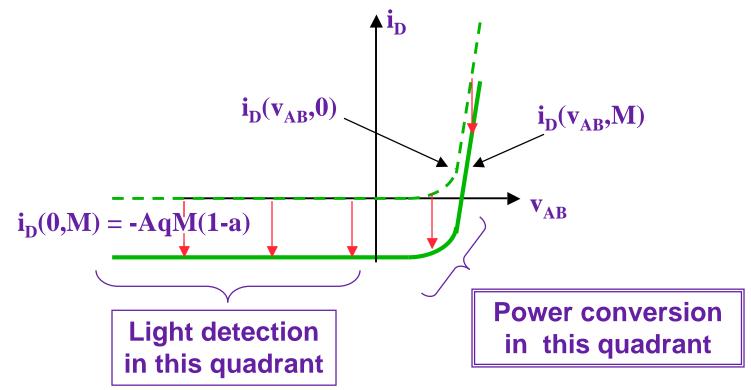

## **Solar Cells:** Illumination shifts diode curve downward Electrical power is produced in 4th quadrant

The total current:

$$i_D(v_{AB}, M) = i_D(v_{AB}, 0) + i_D(0, M)$$

=  $I_S(e^{qv_{AB}/kT} - 1) - AqM(1 - a)$

Illumination shifts the ideal diode curve down vertically:

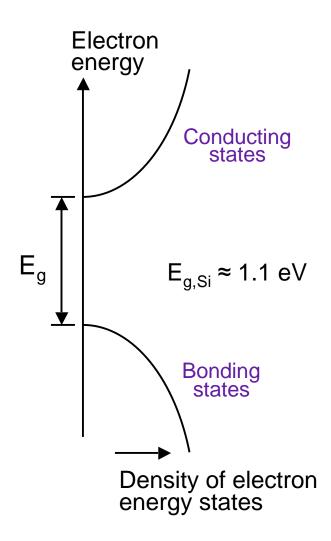

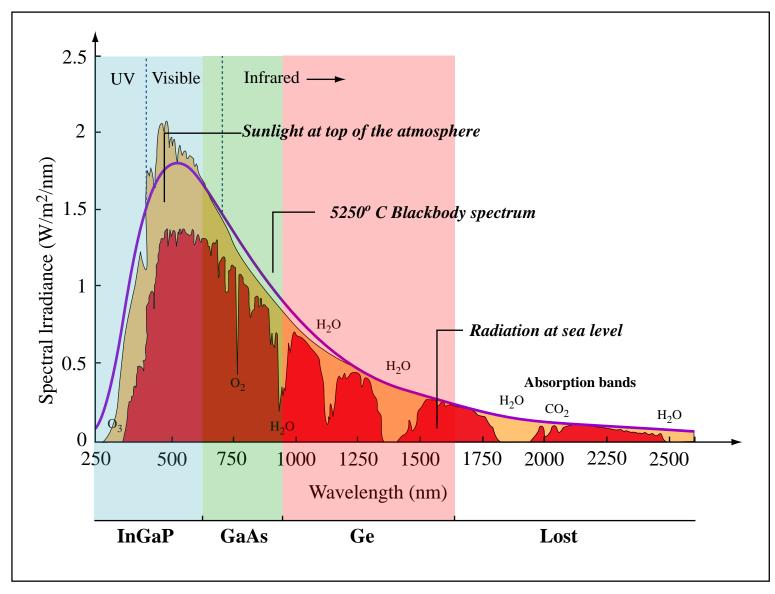

# Solar Cells: A single band-gap diode misses much of the solar energy spectrum

Photons with energy, hv, <u>less</u> than  $E_g$  are not absorbed, and that part of the spectrum is lost.

Photons with energy, hv, more <u>than E<sub>g</sub></u> are absorbed but all their energy above E<sub>g</sub> is lost to the crystal lattice as the electrons and holes "relax" to the bottom of their the lowest energy states. This limits Si solar cell efficiency to ~ 20%.

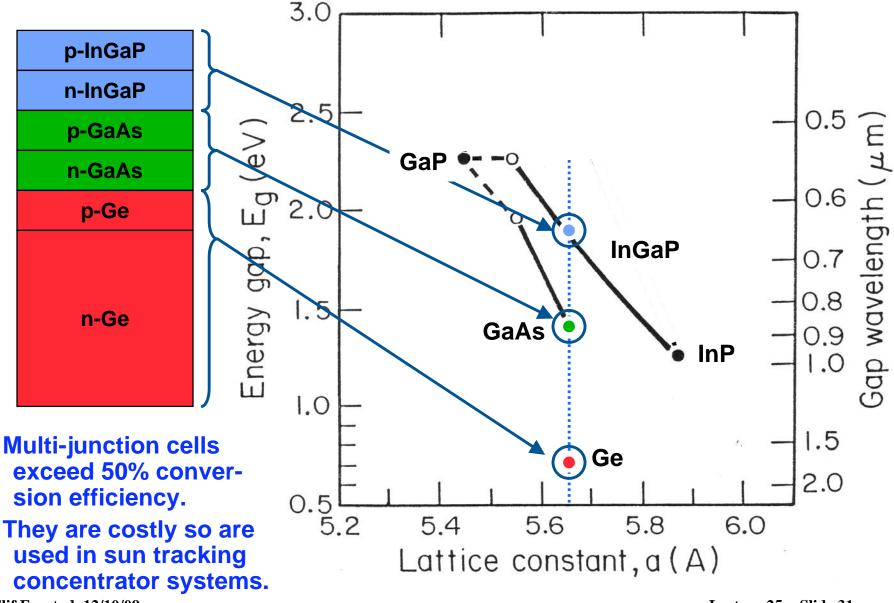

The solution: Stack (layer) several solar cells with differing band-gaps so each optimally absorbs the optimum range of photons.

**Solar Cells:** Multi-junction solar cells InGaP/GaAs/Ge

Clif Fonstad, 12/10/09

# **Solar Cells:** Multi-junction solar cells InGaP/GaAs/Ge, cont.

Figure by MIT OpenCourseWare.

Clif Fonstad, 12/10/09

Life after 6.012 - cont.

| • | Proce: 6.152J:                       | ssing<br>Microelectronics processing technology                                                                                                          |             | U(F,S)                                |

|---|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------|

|   | 6.778J:<br>6.780J:                   | Physics of fabrication: front-end proc.<br>Materials and processes for MEMS<br>Control of manufacturing processes<br>Sub-micron and nanometer technology | H<br>H<br>H | G(F*)<br>G(S)<br>G(S*)<br>G(S)        |

| • | 6.301:<br>6.302:<br>6.331:<br>6.334: | g circuits<br>Solid-state circuits<br>Feedback systems<br>Advanced circuit techniques<br>Power electronics<br>Low power analog VLSI                      | H<br>H<br>H | G(F)<br>G(S)<br>G(F*)<br>G(S)<br>G(F) |

|   | 6.775:<br>6.776:                     | Design of analog MOS LSI<br>High speed communications circuits                                                                                           | H<br>H      | G(S)<br>G(S*)                         |

| • | Digita                               | l circuits                                                                                                                                               |             |                                       |

|   |                                      | Analysis and design of digital ICs<br>Complex Digital Systems Design                                                                                     | H<br>H      | G(F)<br>G(S)                          |

Clif Fonstad, 12/10/09

6.012 - Microelectronic Devices and Circuits

Lecture 25 - Beyond Si; Beyond 6.012 - Summary

### • The current state-of-the-art

6.012 Microelectronic Devices and Circuits Fall 2009

For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.